ISOFIC 2014 2014.08.24~08.28, Jeju

### An Integrated Software Development Framework for PLC & FPGA based Digital I&Cs

Junbeom Yoo, Eui-Sub Kim, Dong Ah Lee KONKUK University

and

**Jong-Gyun Choi** Korea Atomic Energy Research Institute (KAERI)

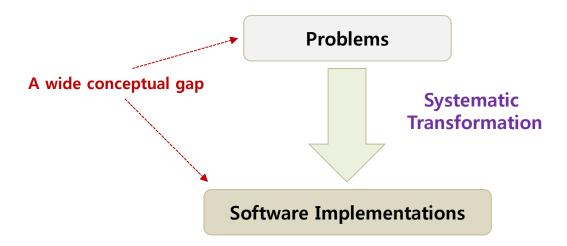

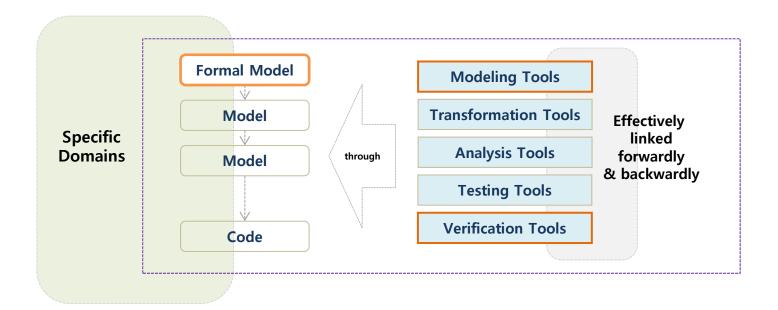

### Model-Based Development for I&C Software

#### **MBD**(Model-Based Development)

- : Software development approaches in which abstract models of software systems are created and systematically transformed to concrete implementations

- Reducing the gap between problem and software implementation domain

- Using technologies that support systematic transformation of problem-level abstractions to software implementations

- Using models that describe complex systems at multiple levels of abstraction through automated support for transforming and analyzing models

### MBD for I&Cs

Highly recommended to systematically cope with standards and regulations on software safety

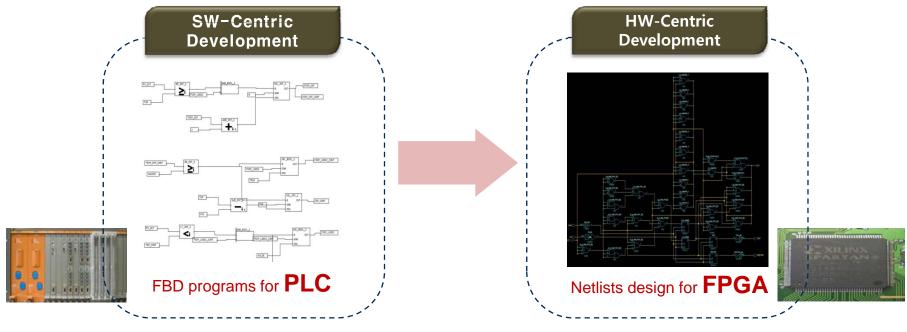

#### The Platform Change of Digital I&Cs from PLC to FPGA

In order to reduce the maintenance cost of PLCs and use more computation power than PLCs

However, it is too risky!

It is not the change of SW development methods, but that of development paradigms.  $PLC \rightarrow FPGA = CPU$ -based Software  $\rightarrow$  Net-based Hardware

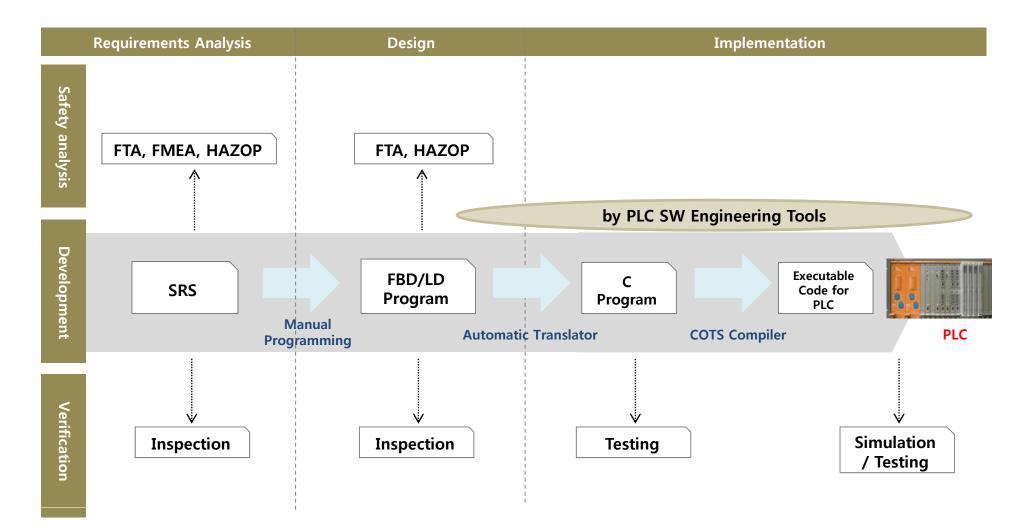

#### **Typical Software Development Process for PLC-based I&Cs**

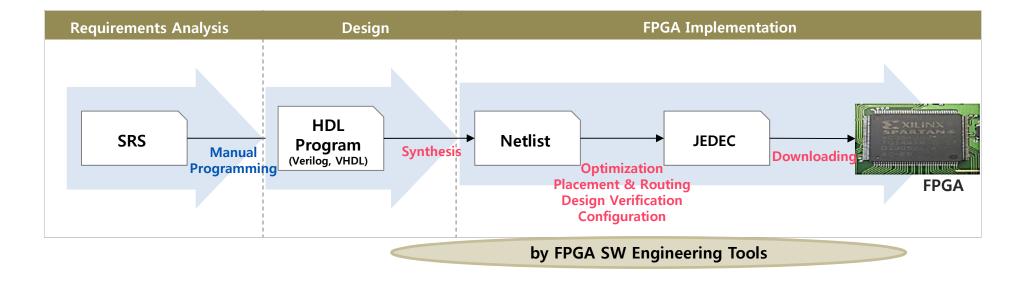

### **Typical Software Development Process for FPGA**

The parallel processes for safety analysis and verification as the PLC have not yet been defined for safe-level I&C Applications!!!

No commercial FPGA implementation for RPS or ESF-CCS, yet.

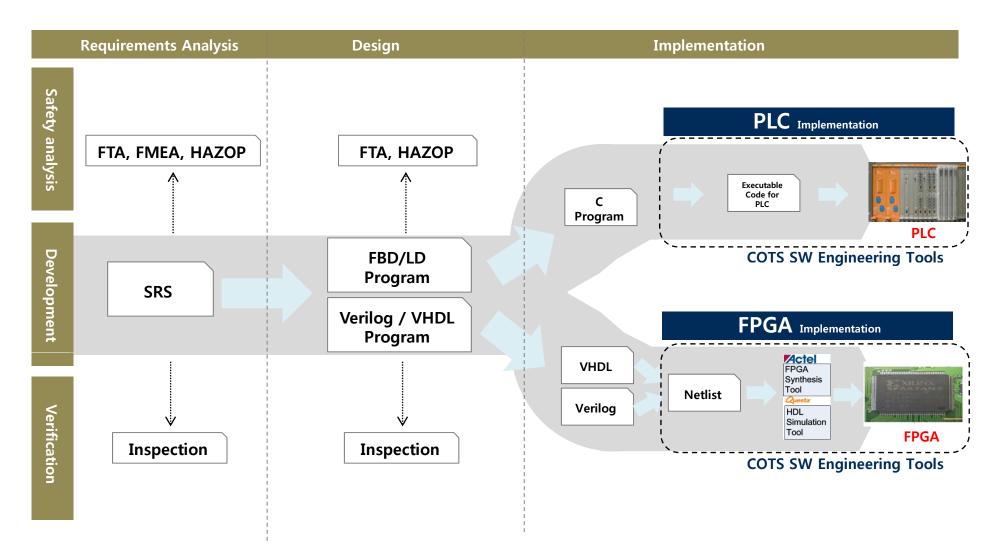

### An Overlap of Two SW Development Processes

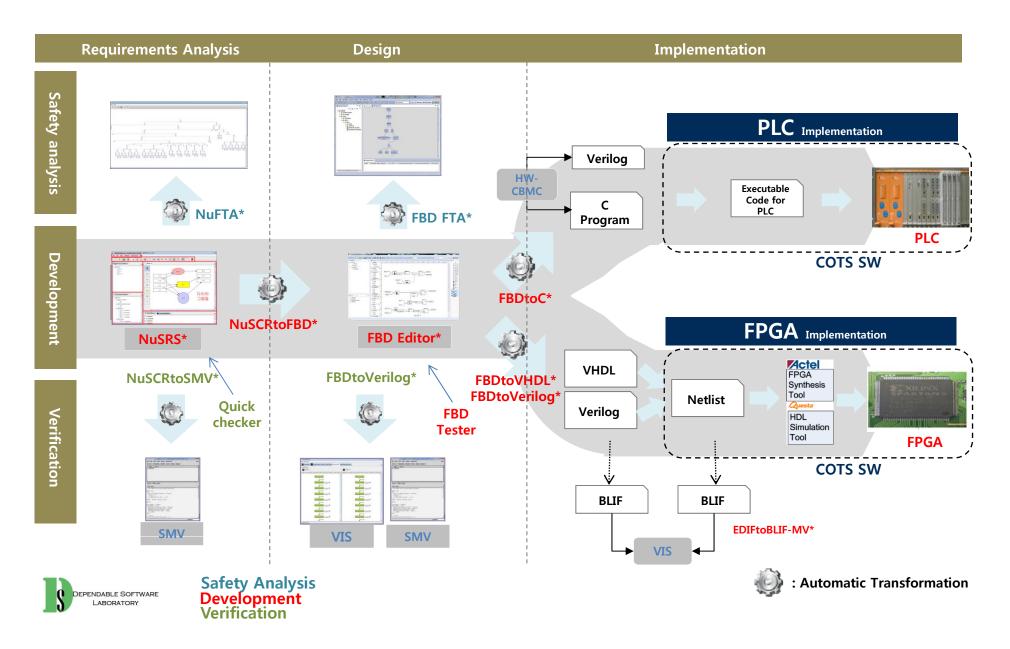

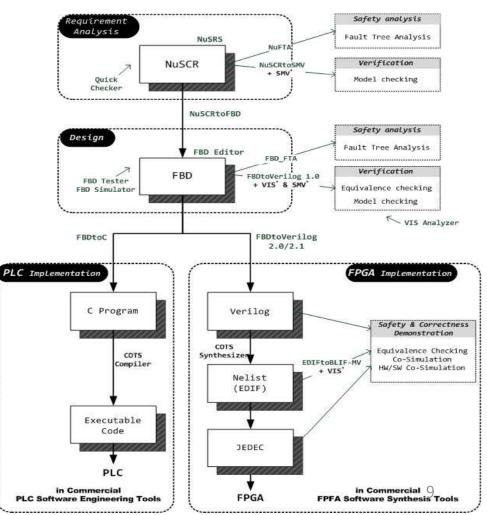

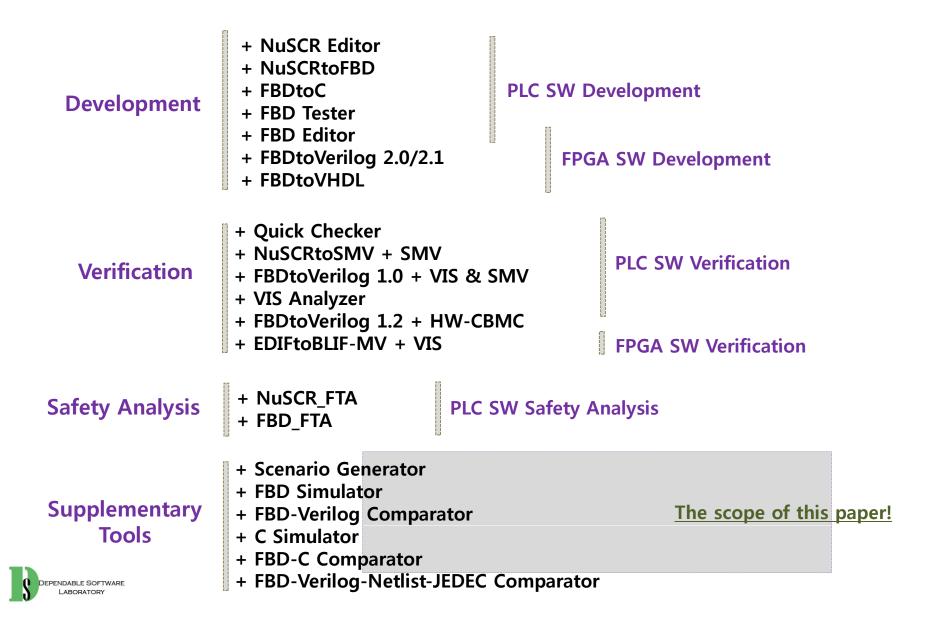

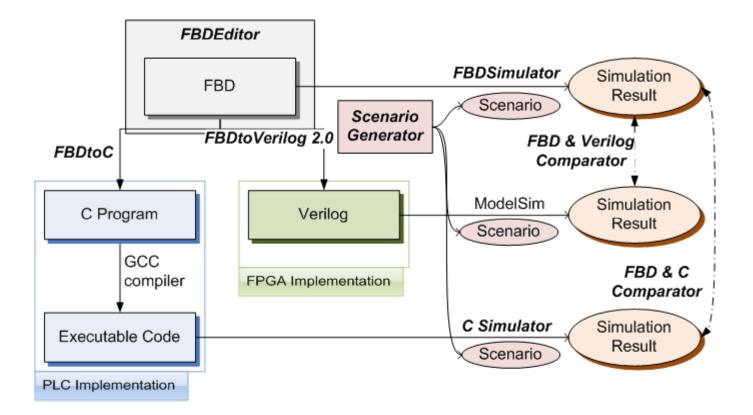

### The Scope of NuDE 2.0

### An Overview of NuDE 2.0

- NUDE (Nuclear Development Environment) 2.0

- An formal methods-based MBD for Digital I&C software

- Target platforms: PLC & FPGA

- Starting from a formal SRS in NuSCR

- Supporting various V&V methods

- Model Checking

- Equivalence Checking

- Considering safety demonstration of commercial SW synthesis tools

- From an SRS in NuSCR or SDS in FBD, the PLC and FPGA implementations can be generated simultaneously.

#### **The NuDE Components**

# **DEVELOPMENT PROCESS**

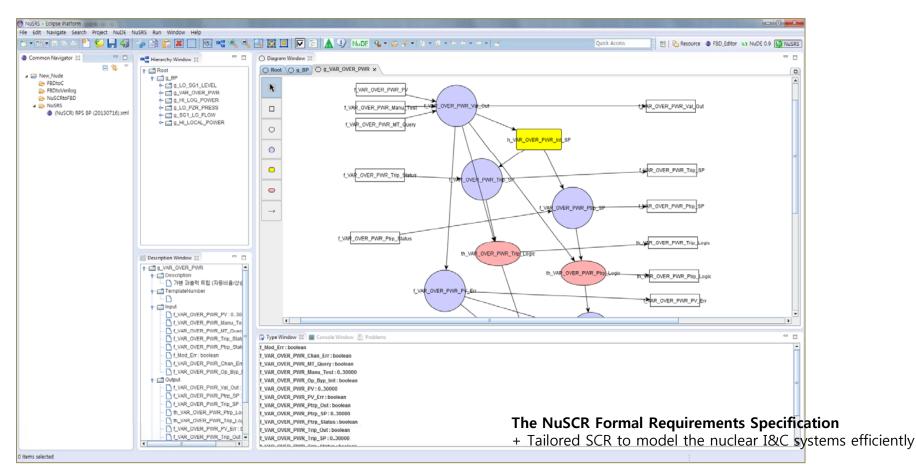

#### NuSCR Editor (NuSRS 2.0)

#### The NuSCR Elements

- + FOD (Function Overview Diagram)

- + SDT (Structured Decision Table)

- + FSM (Finite State Machine)

- + TTS (Timed Transition System)

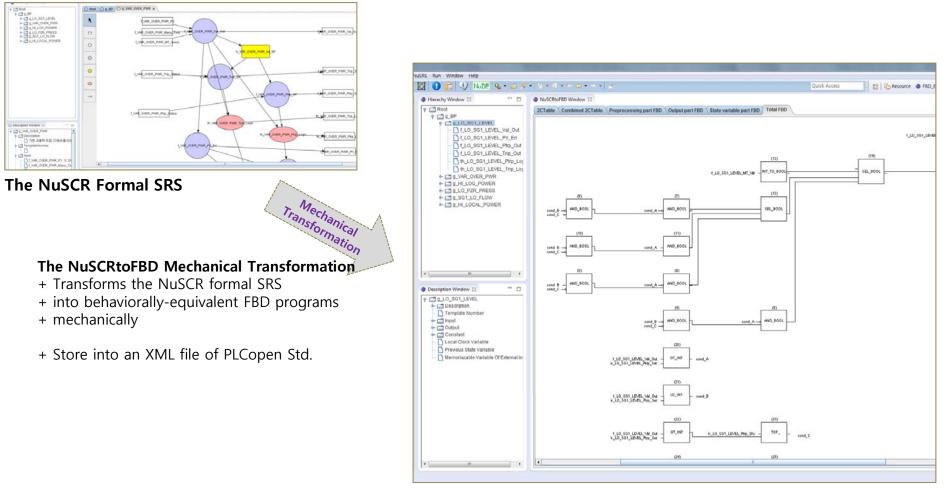

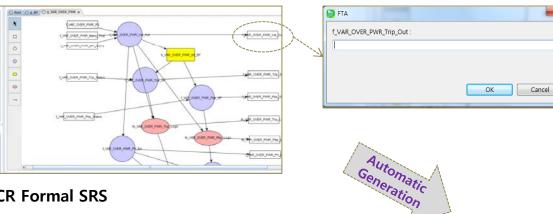

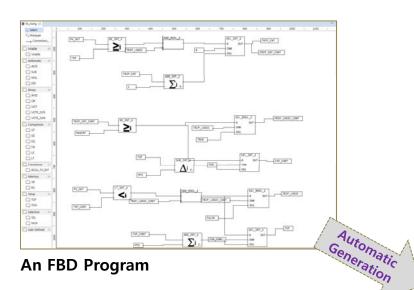

### NuSCRtoFBD (Ver. 3.0)

**FBD Program**

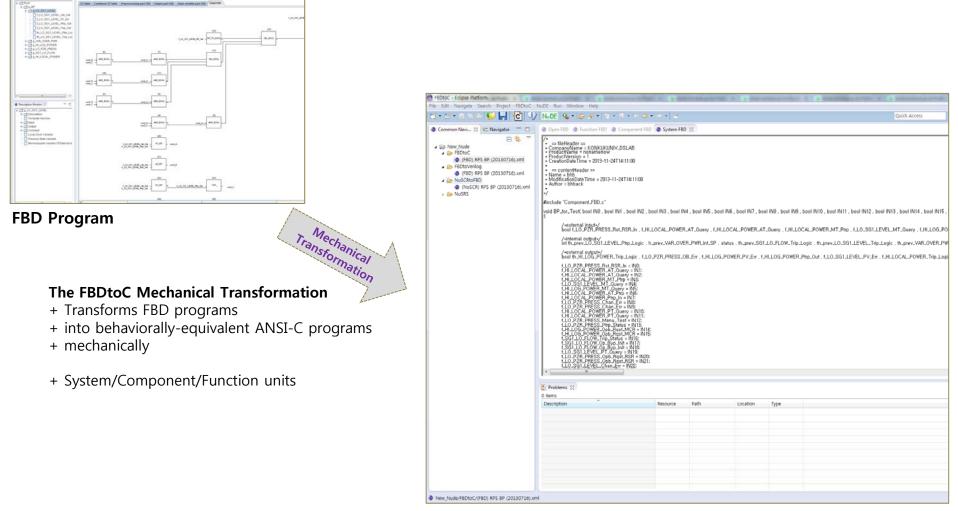

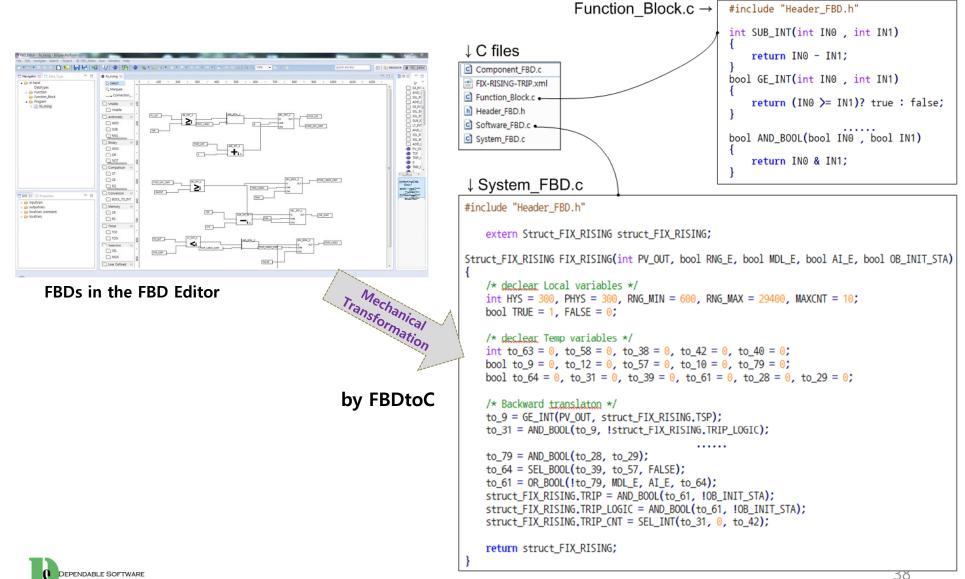

### FBDtoC (Ver. 1.0)

**C** Program

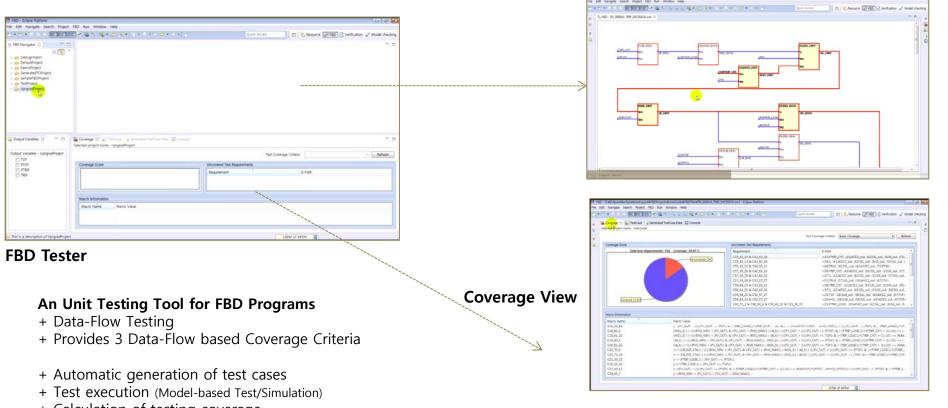

#### FBD Tester (of Prof. Gee in KAIST)

#### **FBD Test Execution**

| + Calculation | OT | testing | coverage |  |

|---------------|----|---------|----------|--|

|               |    |         |          |  |

+ Reads an FBD program in an XML file of PLCopen Std.

| overage g     | , TestCase    | Generated T   | estCase Data 🔀 | Console       |           |           |                |                |

|---------------|---------------|---------------|----------------|---------------|-----------|-----------|----------------|----------------|

| cted project  | t name : User | Guide         |                |               |           |           |                |                |

|               |               |               |                |               |           |           |                |                |

| est case inf  | ormation      |               |                |               |           |           |                |                |

|               |               |               |                |               |           | -         |                |                |

| PV OUT        | PTSP          | TSP           | PTRIP_LOG      | TRIP_LOGIC    | PTRIP_CNT | TRIP_CNT  | ALE            | MDL E          |

| -             |               |               |                |               |           |           |                | -              |

| -301          | 300           | -300          | true           | true          | 301       | 303       | false          | false          |

| -301<br>29400 | 300<br>29400  | -300<br>29400 | true<br>false  | true<br>false | 301<br>0  | 303<br>-2 | false<br>false | false<br>false |

Output Variables 3

lutput Variable

#### **Test Case Generation**

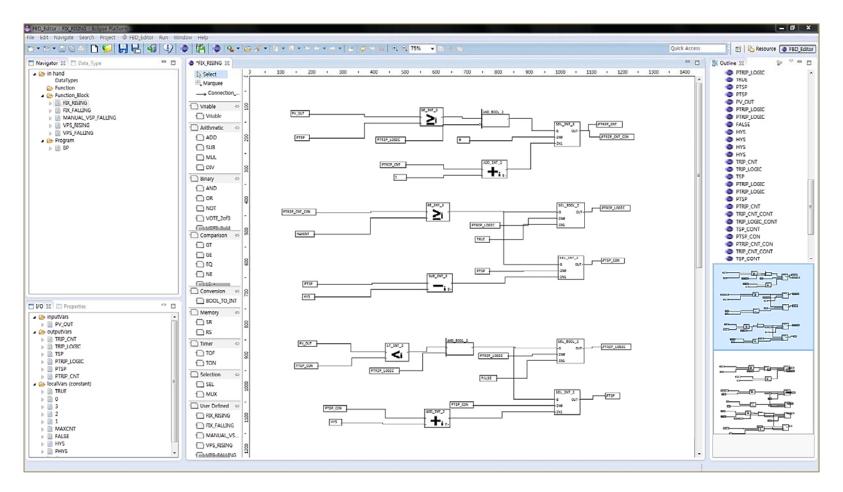

#### **FBD Editor**

#### The FBD Program Editor

- + Programming FBD programs of IEC 61131-1 Std.

- + Reads and stores an XML file of PLCopen Std.

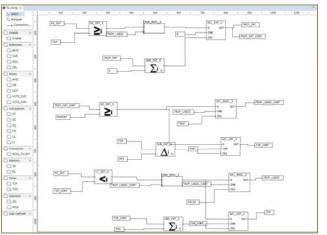

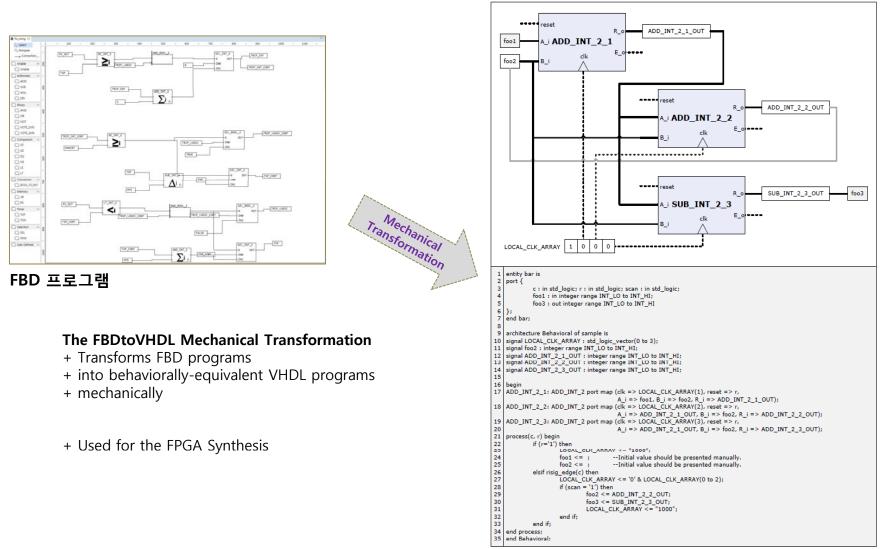

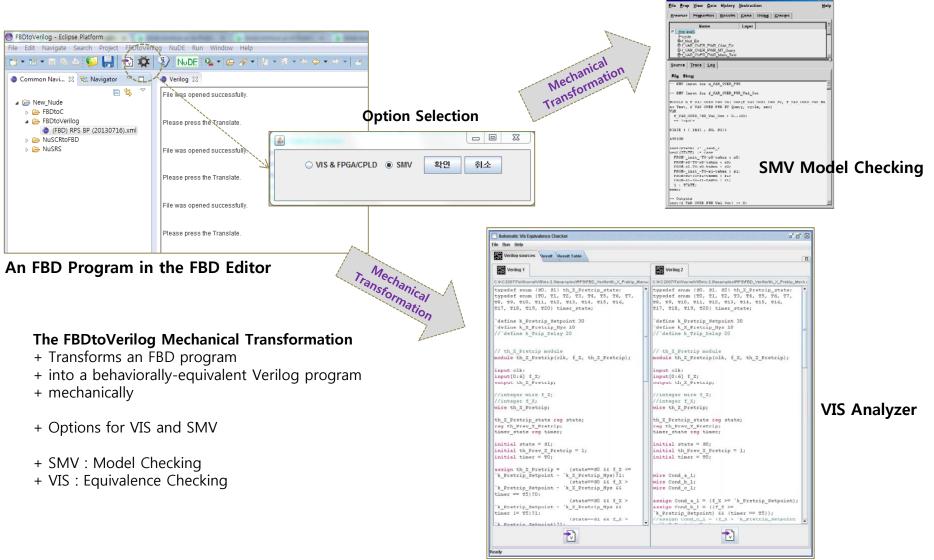

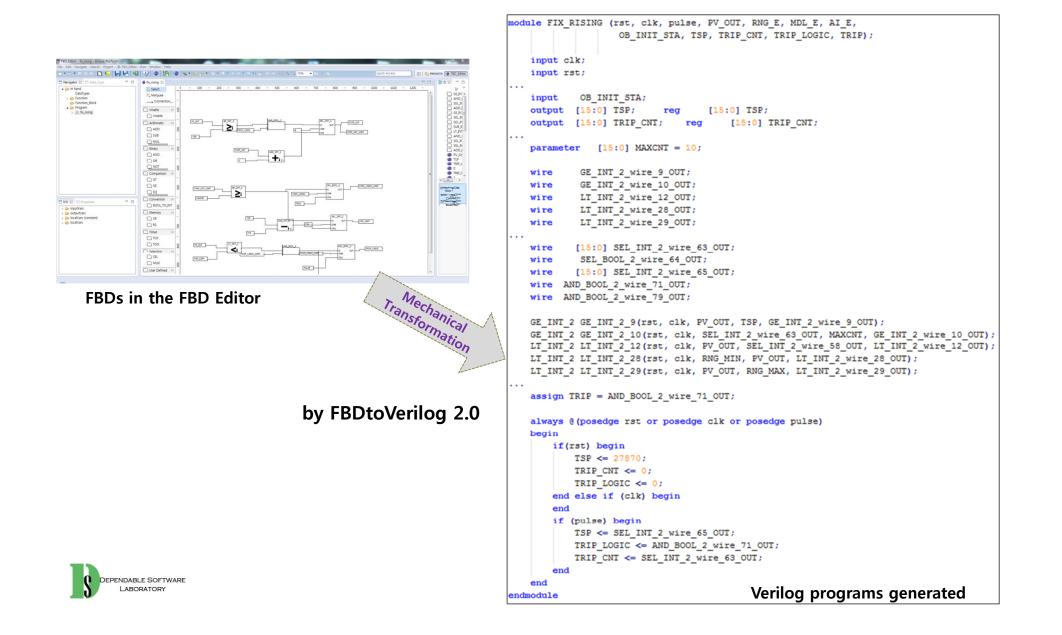

### FBDtoVerilog 2.0/2.1

**FBD Program**

#### The FBDtoVerilog Mechanical Transformation

- + Transforms FBD programs

- + into behaviorally-equivalent Verilog programs

- + mechanically

- + Used for the FPGA Synthesis

```

DEPENDABLE SOFTWARE

LABORATORY MICROSEMI - Libero

Netlist View

```

input clk; input rst; input [31:0] PV\_OUT; output [31:0] TRIP\_CNT; reg [31:0] TRIP\_CNT; TRIP LOGIC; output TRIP LOGIC; reg output [31:0] TSP; rea [31:0] TSP; parameter TRUE = 1; false = 0; parameter parameter [31:0] MAXCNT = 30; rea [31:0] HYS = 300; GE\_INT\_2\_wire\_1\_OUT; wire wire AND\_BOOL\_2\_wire\_2\_OUT; [31:0] SEL\_INT\_2\_wire\_3\_OUT; wire [31:0] ADD\_INT\_2\_wire\_4\_OUT; wire wire ADD\_INT\_2\_wire\_4\_E; GE\_INT\_2\_wire\_14\_OUT; wire SEL BOOL 2 wire 15 OUT; wire wire [31:0] SEL\_INT\_2\_wire\_16\_OUT; [31:0] SUB INT 2 wire 17 OUT; wire SUB\_INT\_2\_wire\_17\_E; wire wire LT\_INT\_2\_wire\_27\_OUT; GE\_INT\_2 GE\_INT\_2\_1(rst, clk, PV\_OUT, TSP, GE\_INT\_2\_wire\_1\_OUT); AND BOOL 2 AND BOOL 2 2 (rst, clk, GE\_INT 2 wire 1 OUT, ~TRIP LOGIC, AND BOOL 2 wire 2 SEL\_INT\_2 SEL\_INT\_2\_3 (rst, clk, AND\_BOOL\_2\_wire\_2\_OUT, 0, ADD\_INT\_2\_wire\_4\_OUT, SEL\_IN ADD\_INT\_2 ADD\_INT\_2\_4(rst, clk, TRIP\_CNT, 1, ADD\_INT\_2\_wire\_4\_OUT, ADD\_INT\_2\_wire\_4\_E) GE\_INT\_2 GE\_INT\_2\_14(rst, clk, TRIP\_CNT\_CONT, MAXCNT, GE\_INT\_2\_wire\_14\_OUT); SEL BOOL 2 SEL BOOL 2 15 (rst, clk, GE INT 2 wire 14 OUT, TRIP LOGIC, TRUE, SEL BOOL 2 SEL\_INT\_2 SEL\_INT\_2\_16(rst, clk, GE\_INT\_2\_wire\_14\_OUT, TSP, SUB\_INT\_2\_wire\_17\_OUT, SEI SUB\_INT\_2 SUB\_INT\_2\_17(rst, clk, TSP, HYS, SUB\_INT\_2\_wire\_17\_OUT, SUB\_INT\_2\_wire\_17\_E) LT\_INT\_2 LT\_INT\_2\_27(rst, clk, PV\_OUT, TSP\_CONT, LT\_INT\_2\_wire\_27\_OUT); AND BOOL 2 AND BOOL 2 28 (rst, clk, LT\_INT 2 wire 27 OUT, TRIP\_LOGIC\_CONT, AND BOOL 2 v SEL\_INT\_2 SEL\_INT\_2\_29(rst, clk, AND\_BOOL\_2\_wire\_28\_OUT, TSP\_CONT, ADD\_INT\_2\_wire\_31\_C SEL BOOL 2 SEL BOOL 2 30 (rst, clk, AND BOOL 2 wire 28 OUT, TRIP LOGIC CONT, FALSE, SEI ADD\_INT\_2 ADD\_INT\_2\_31(rst, clk, TSP\_CONT, HYS, ADD\_INT\_2\_wire\_31\_OUT, ADD\_INT\_2\_wire assign TRIP\_CNT\_CONT = SEL\_INT\_2\_wire\_3\_OUT; assign TRIP LOGIC CONT = SEL BOOL 2 wire 15 OUT; assign TSP\_CONT = SEL\_INT\_2\_wire\_16\_OUT; always @(posedge rst or posedge clk) begin if(rst) begin TRIP\_CNT <= 16'50000000000000000; TRIP\_LOGIC <= 1'b0;</pre> TSP <= 26805; end else if (clk) begin TRIP CNT <= SEL INT 2 wire 3 OUT; TRIP\_LOGIC <= SEL\_BOOL\_2\_wire\_30\_OUT;</pre> TSP <= SEL\_INT\_2\_wire\_29\_OUT;</pre> end

wodule fix\_rising (rst, clk, PV\_OUT, TRIP\_CNT, TRIP\_LOGIC, TSP);

end

Verilog Program

### **FBDtoVHDL**

VHDL program

# **VERIFICATION PROCESS**

### **Quick Checker**

The NuSCR Formal SRS

#### Static Analysis (Rule Checking) on the NuSCR formal SRS

+ Checking for the C&C(Completeness & Consistency) requirements

| Type Window Console Window 🔽 Quick Check of Root 🗙              | (        |

|-----------------------------------------------------------------|----------|

| Error At Root, Node f_VAR_OVER_PWR_Val_Out_i has no transition. | <b>^</b> |

| Error At g_BP, Node h_VAR_OVER_PWR_Int_SP has no transition.    | =        |

| Error At g_TEST_SEL, Node f_PT_Gen has no transition.           |          |

| Error At g_TEST_SEL, Node f_BS01_MT_Query has no transition.    |          |

| Error At g TEST SEL, Node f OB MT Query has no transition.      | -        |

|                                                                 | •        |

A result of Quick Checker

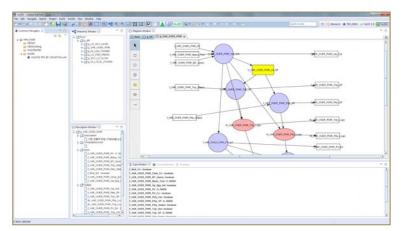

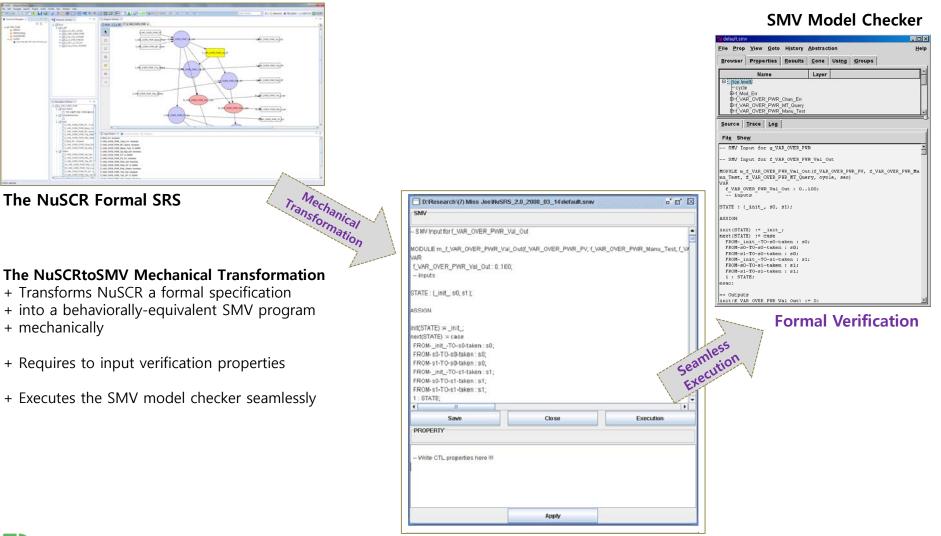

#### NuSCRtoSMV + SMV

**SMV Input Program**

#### FBDtoVerilog 1.0 + VIS & SMV

VIS Equivalence Checking

#### & the Execution Result

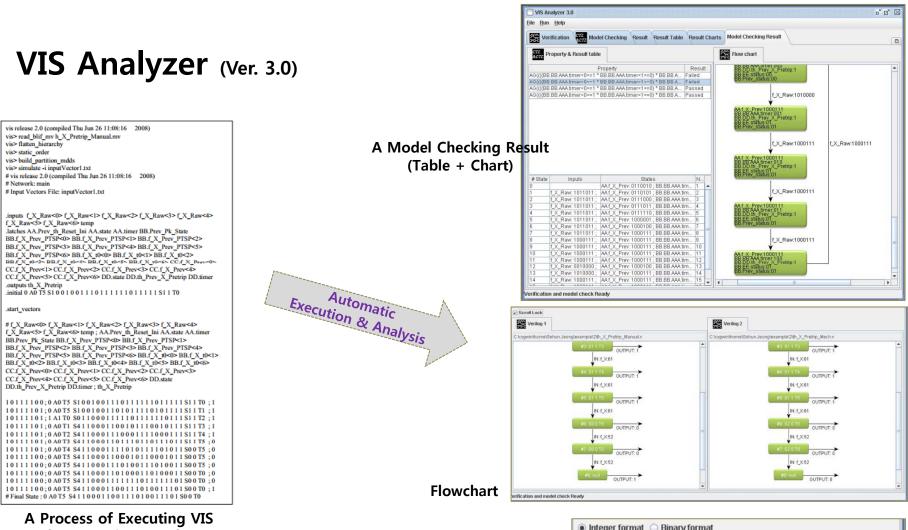

#### VIS Analyzer

- + To use/execute the VIS efficiently

- + The VIS has no GUI

- + Display the verification results in various forms

| # state | input   | File1Output | File2Output | File1State | File2State |

|---------|---------|-------------|-------------|------------|------------|

| 0       | Initial | Initial     | Initial     | S1 1 T0    | S0 1 T0    |

| 1       | f_X:61  | 1           | 1           | S1 1 T1    | S1 1 T1    |

| 2       | f_X:61  | 1           | 1           | S1 1 T2    | S1 1 T2    |

| 3       | f_X:61  | 1           | 1           | S1 1 T3    | S1 1 T3    |

| 4       | f_X:61  | 1           | 1           | S1 1 T4    | S1 1 T4    |

| 5       | f_X:61  | 1           | 1           | S1 1 T5    | S1 1 T5    |

| 6       | f_X:61  | 0           | 0           | S0 0 T5    | S2 0 T5    |

| 7       | f_X:52  | 0           | 0           | S0 0 T0    | S2 0 T0    |

| 8       | f X:52  | 1           | 0           | Null       | Null       |

Table

- 0 ×

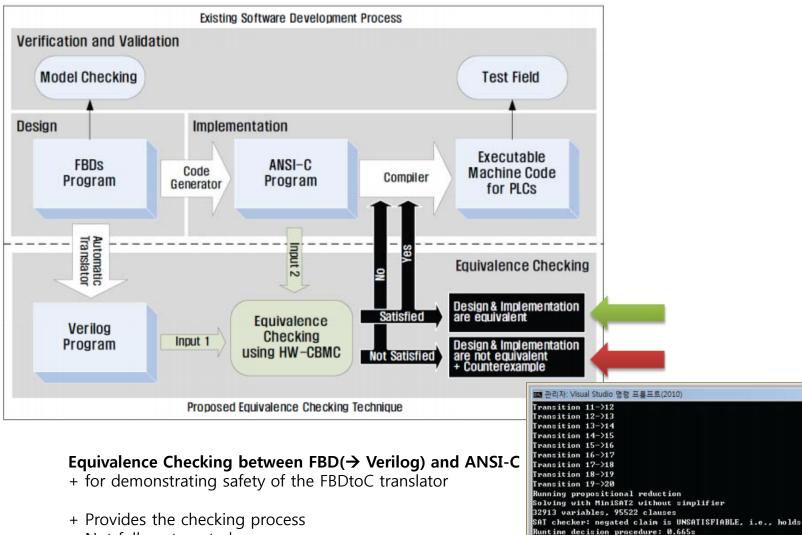

### **FBDtoVerilog + HW-CBMC**

VERIFICATION SUCCESSFUL

D:#DSLAB#CBMC#CBMC namual#example>

+ Not fully automated

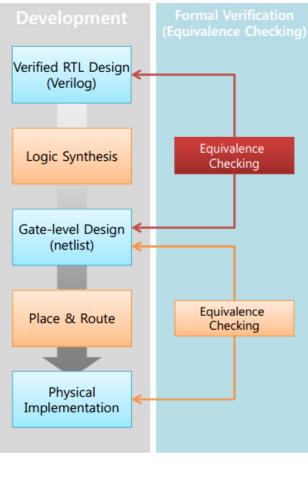

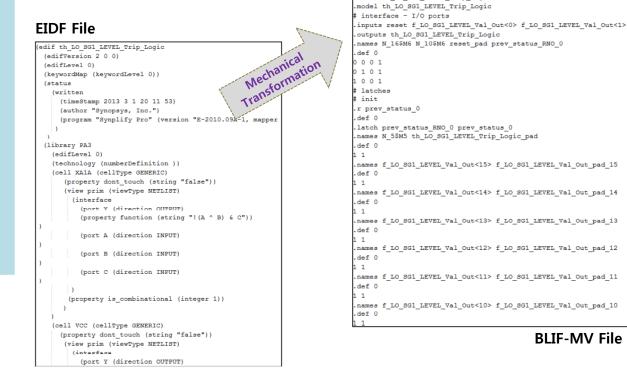

#### EDIFtoBLIF-MV + VIS

DEPENDABLE SOFTWARE LABORATORY

#### The VerilogtoBLIF-MV Mechanical Transformation

- + For the equivalence checking between Verilog and Netlist

- + For the safety demonstration of FPGA Synthesis tools

- + Transforms a Netlist (in EDIF format) into a program of BLIF-MV format

cell th LO SG1 LEVEL Trip Logic

+ Then performs the VIS Equivalence Checking

# SAFETY ANALYSIS PROCESS

### **NuSCR FTA**

+ We need to define the value of an output variable

×

The NuSCR Formal SRS

+ Generates a fault tree + from an NuSCR formal SRS

+ Calculates (minimal) cut-sets

The NuSCRtoFT Mechanical Generation

+ for a specific (important) output variable

Contractions + Contractions D 3/2 Sec 65 (Venuer

+ 12

# NuFTA 1.0 View Help 0000

FT (Fault Tree)

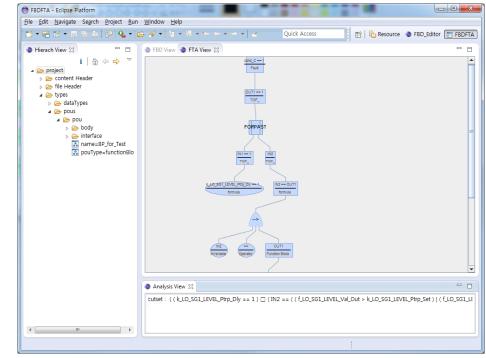

### **FBD FTA**

#### The FBDtoFT Mechnical Generation

- + Generates a fault tree

- + from an FBD program

- + for a specific (important) output variable

- + Calculates (minimal) cut-sets

- + Uses the Temporal Fault Tree semantics

- + Under developing the minimal cut-set optimization

FT (Fault Tree)

# SUPPLEMENTARY TOOLS

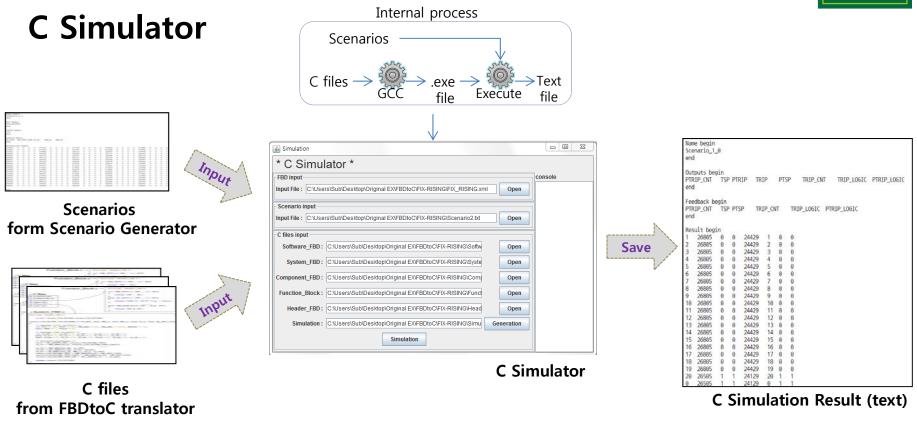

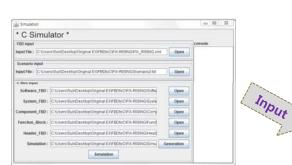

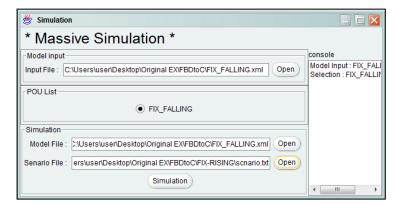

#### **C** Simulator

- + Compiles an inputted C program from FBDtoC translator

- + with GCC compiler into executable file

- + Simulates an executable file from GCC compiler

- + with a inputted Scenarios from Scenario Generator

- + Saves a result of simulation into text file

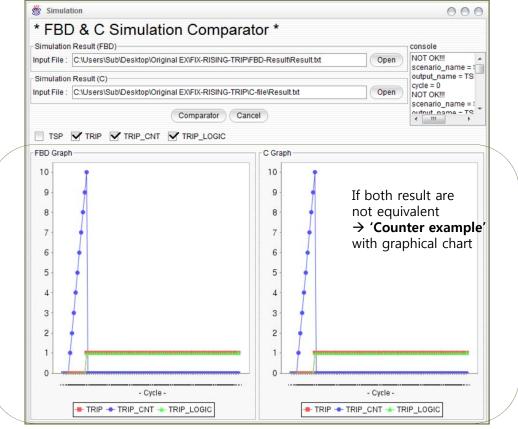

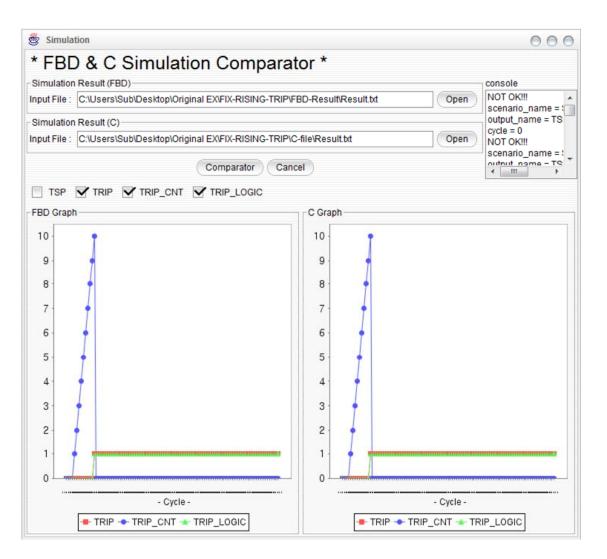

### **FBD-C Comparator**

#### **C** Simulator

| 😤 Simulation                                                                                                                                                                      |                                                           | 1              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|

| * Massive Simulation *                                                                                                                                                            |                                                           | and the second |

| Model Input Input File : C1Usersluser/Desktop/Original EXF8DtoC/FiX_FALLING.xml Open)                                                                                             | console<br>Model Input : FD_FALI<br>Selection : FD_FALLIP | Input          |

| POULIst                                                                                                                                                                           |                                                           | 1 martine      |

| Simulation Model File: [UsersTuser/Destop/Onginal EXFEDITO/FIX_FALLING xm] Open Senarto File: [essuser/Destop/Onginal EXFEDITO/FIX_FALSINGuscnario tal] Simulation ] Simulation ] |                                                           |                |

**FBD Simulator**

**FBD-C Comparator**

#### **BD-C Comparator**

- + Compares between simulation result from C simulator and FBD simulator

- + If both result are equivalent, it produce the 'True'

- + Otherwise, it produce a counter example with graphical chart

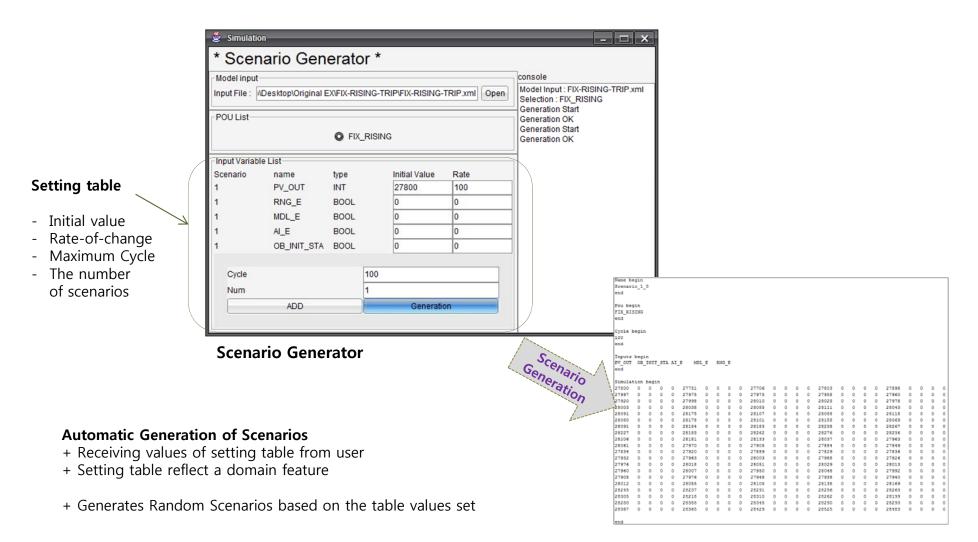

### **FBD Scenario Generator**

#### **FBD Simulator**

Type A

Scenario Generator with graphical chart

#### The Scenario Generator with graphical chart

- + Receives value from user in one cycle

- + Simulates one by one cycle

- + Results in graphical chart  $\rightarrow$  It can verify function of an FBD

#### Туре В

#### Scenario Generator for massive scenario

#### The Scenario Generator for massive scenario

- + Receives scenarios from Scenario Generator and FBD

- + Simulates massive scenarios

- + Results in a text file

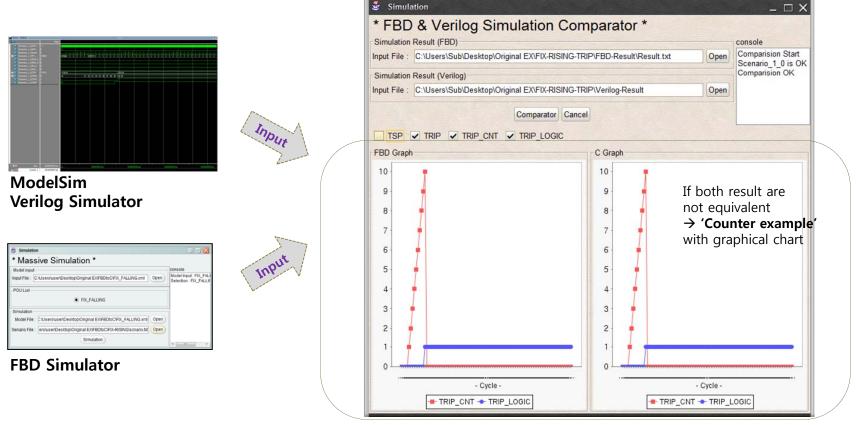

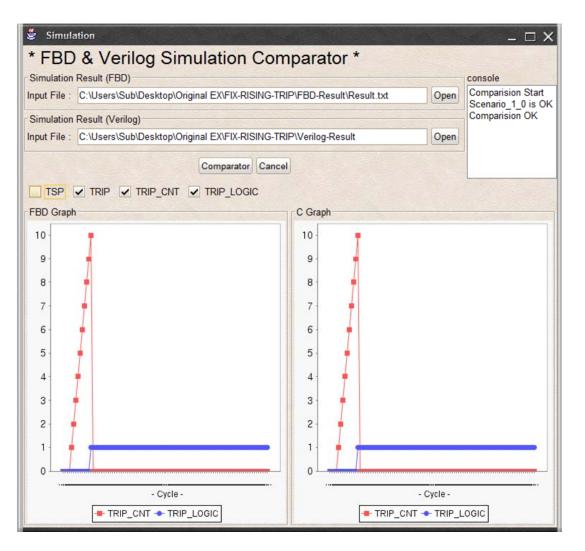

#### **FBD-Verilog Comparator**

**FBD-Verilog Comparator**

#### The FBD-Verilog Comparator

- + Compare between simulation results from ModelSim and the FBD simulator

- + If both result are equivalent, it produce the 'True'

- + Otherwise, it produces a counter example with graphical chart

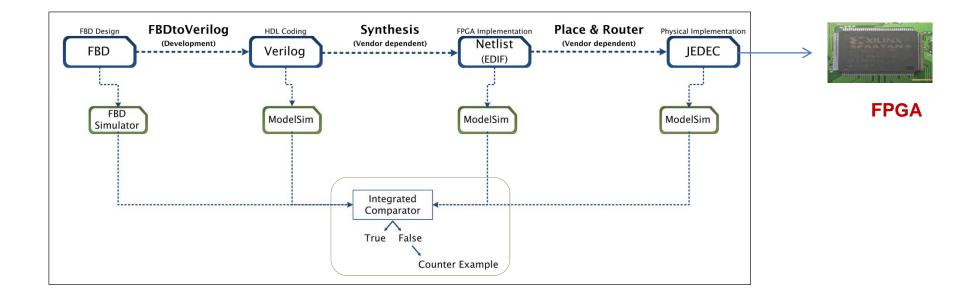

### **FBD-Verilog-Netlist-JEDEC Comparator**

Future Work !!

#### The Integrated Comparator for (FBD-Verilog-Netlist-JEDEC) synthesis process

- + Receives variable simulation results from FBD, Verilog, Netlist and JEDEC simulations

- + It will provide user more efficient verification environment for developing FPGA software

# THE CASE STUDY IN THE PAPER

### The Case Study in the Paper

Goal: Validate the correctness of two transformations (FBDtoC and FBDtoVerilog 2.0)

#include "Header\_FBD.h"

### The FBDtoC Transformation

LABORATORY

C programs generated

### The FBDtoVerilog Transformation

### **Scenario Generator**

| 🖉 Simulatio  | on                      |              |                    |                  |                                                                  | -                                                                                                                                                                        |                                                                             | ×                                       |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

|--------------|-------------------------|--------------|--------------------|------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------|---|

| * Scer       | nario Gen               | erator       | *                  |                  |                                                                  |                                                                                                                                                                          |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| Model input  |                         |              |                    |                  | console                                                          |                                                                                                                                                                          |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

|              |                         | EX/FIX-RISIN | G-TRIP\FIX-RISING- | TRIP.xml Open    | Model Input : Fix                                                | RISING                                                                                                                                                                   | G-TRIP.                                                                     | xml                                     |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| POU List     |                         | FIX_RI       | ISING              |                  | Generation St<br>Generation Of<br>Generation St<br>Generation Of | art                                                                                                                                                                      |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| Input Variab | le List                 |              |                    |                  |                                                                  |                                                                                                                                                                          |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| Scenario     | name                    | type         | Initial Value      | Rate             |                                                                  |                                                                                                                                                                          |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| 1            | PV_OUT                  | INT          | 27800              | 100              |                                                                  |                                                                                                                                                                          |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| 1            | RNG_E                   | BOOL         | 0                  | 0                |                                                                  |                                                                                                                                                                          |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| 1            | MDL_E                   | BOOL         | 0                  | 0                |                                                                  | Name be                                                                                                                                                                  | gin                                                                         |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| 4            | AI_E                    | BOOL         | 0                  | 0                |                                                                  | Scenari                                                                                                                                                                  |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| 4            | OB_INIT_STA             |              | 0                  | 0                |                                                                  | end                                                                                                                                                                      |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

|              | 00_1111_01X             | DOOL         | 0                  | 0                |                                                                  | Pou beg                                                                                                                                                                  |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| Cuala        |                         | 10           | 20                 |                  |                                                                  | FIX_RIS<br>end                                                                                                                                                           | ING                                                                         |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| Cycle        |                         | -            |                    |                  |                                                                  | Cycle b                                                                                                                                                                  |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

| Num          |                         | 1            |                    |                  |                                                                  | 100                                                                                                                                                                      | egin                                                                        |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

|              | ADD                     |              | Generati           | on               |                                                                  | end                                                                                                                                                                      |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

|              |                         |              |                    |                  |                                                                  | Inputs                                                                                                                                                                   |                                                                             |                                         |                                                                                                                                                                                                                              |      |       |     |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

|              |                         |              |                    |                  |                                                                  | PV_OUT<br>end                                                                                                                                                            | OB_INI                                                                      | T_STA                                   | AI_E MI                                                                                                                                                                                                                      | DL_E | RNG_I | E   |                                                                                                                                              |   |                                                                                                                                                                                                                                                                                                                                                                                   |                                         |                                                                                                                                                                                           |   |     |                                                                                                                                                       |                                         |                                                                                             |   |

|              |                         |              |                    | Scene<br>Generat | nion<br>ion                                                      | Simulat<br>27800<br>27997<br>27990<br>28003<br>28091<br>28020<br>28091<br>28227<br>28206<br>28091<br>27834<br>27936<br>27936<br>27936<br>27936<br>2795<br>28012<br>28245 | ion beg<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 | 000000000000000000000000000000000000000 | <ul> <li>28175</li> <li>28178</li> <li>28184</li> <li>28183</li> <li>28181</li> <li>27970</li> <li>27920</li> <li>27920</li> <li>28018</li> <li>28018</li> <li>28027</li> <li>27976</li> <li>28055</li> <li>28237</li> </ul> |      |       |     | 27706<br>27975<br>28010<br>28085<br>28107<br>28101<br>28183<br>28262<br>27905<br>27950<br>27950<br>27950<br>27958<br>28051<br>28105<br>28310 |   | 0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0         0       0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 27803<br>27958<br>28025<br>28111<br>28088<br>28158<br>28258<br>28276<br>28037<br>27829<br>27928<br>28029<br>27928<br>28029<br>27938<br>28028<br>28048<br>27938<br>28138<br>28138<br>28256 |   |     | 27898<br>27960<br>27978<br>28043<br>28118<br>28069<br>28267<br>27963<br>27849<br>27836<br>27926<br>28013<br>27992<br>27940<br>28169<br>28263<br>28199 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |   |

|              | BLE SOFTWARE<br>DRATORY |              |                    |                  |                                                                  | 28280<br>28367<br>end                                                                                                                                                    | 0 0                                                                         | 0                                       | 28358                                                                                                                                                                                                                        | 0    | 0 (   | 0 0 | 28345<br>28429                                                                                                                               | 0 | 0 0                                                                                                                                                                                                                                                                                                                                                                               | 0                                       | 28290<br>28525                                                                                                                                                                            | 0 | 0 0 | 28293<br>28483                                                                                                                                        | 0                                       | 0                                                                                           | 0 |

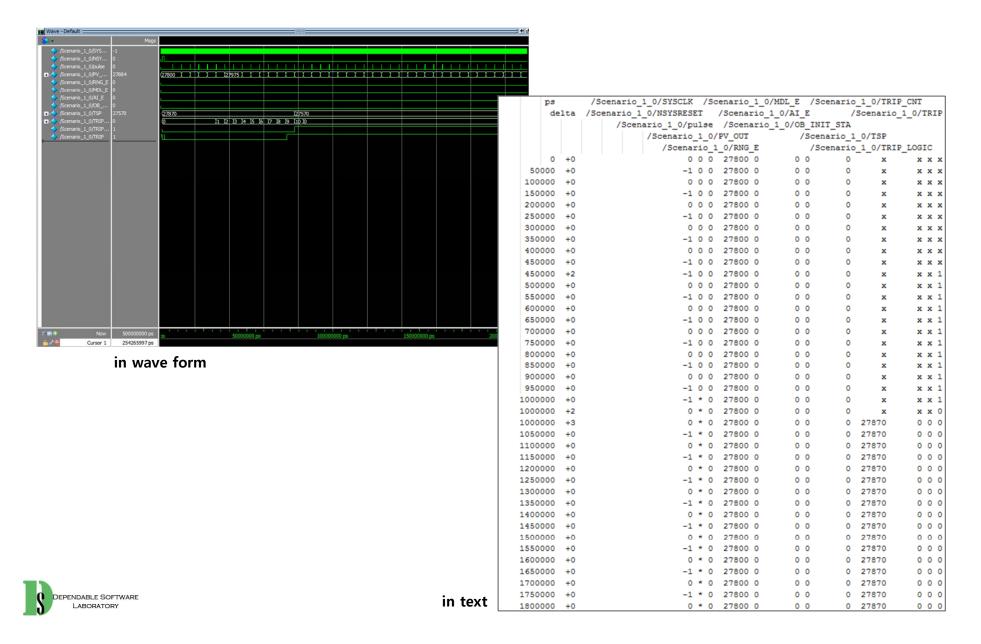

#### **Verilog Simulation with ModelSim**

#### **FBD & Verilog Comparator**

→ The FBDtoVerilog 2.0 transformation worked well!

#### FBD & C Comparator

$\rightarrow$  The FBDtoC transformation worked well!

### **In Summary**

#### NuDE 2.0 can

Provide a systematic MBD-based software development framework for the PLC & FPGA implementations of digital I&Cs, simultaneously

Cope with various standards and regulations in regarding to software safety

Reuse the PLC-based knowledge and experience accumulated for decades

Reduce the risk of the sudden change of SW development paradigm from PLC to FPGA, through starting from the existing FBD programs not HDLs

Be used as a medium of software design diversity to avoid CCF

Consider also the safety demonstration of the commercial SW synthesis tools

# THANK YOU

http://dslab.konkuk.ac.kr jbyoo@konkuk.ac.kr

45