# IP Core Library 사용이 상용 합성도구의 COTS SW Dedication에 미치는 영향 분석

정세진 이 김의섭 1 유준범 1 최종균 2 김장열 2 이장수 2

<sup>1</sup>건국대학교 컴퓨터-정보통신 공학부, <sup>2</sup>한국 원자력 연구원 {jsjj0728, atang34, jbyoo}@konkuk.ac.kr, {choijg,jykim, jslee}@kaeri.or.kr

# The impact analysis of using IP Core library to COTS SW Dedication of Commercial Logic Synthesis tools

Sejin Jung<sup>O1</sup> Eu-Sub Kim<sup>1</sup> Junbeom Yoo<sup>1</sup> Jong-Gyun Choi<sup>2</sup> JangYeol Kim<sup>2</sup> Jang Soo Lee<sup>2</sup>

<sup>1</sup>Division of Computer Science and Engineering, Konkuk University

<sup>2</sup>Korea Atomic Energy Research Institute

#### 요 약

상용 합성도구는 FPGA 개발에 사용되는 소프트웨어로써, RTL(Verilog or VHDL) 로 작성된 디자인을 gate-level 디자인으로 합성하는 역할을 한다. 상용 합성도구를 원자력발전소의 디지털 계측제어 시스템에 사용하기 위해서는 엄격한 기준에 따라 상용 소프트웨어의 인증(COTS SW dedication)이 수행 되어야한다. FPGA 개발에는 설계의 효율성을 위해 IP(Intellectual Property) Core library가 사용 될 수 있으며, 상용 합성 도구의 dedication 시 IP Core library 사용 여부에 대해 고려할 필요가 있다. 이에 본 논문에서는 IP Core library 사용이 상용 합성도구의 COTS SW dedication에 미치는 영향에 대해 분석 하였다.

# 1. 서 론

원자력발전소의 디지털 계측제어 시스템(I&C: Instrumentation and Controller)은 안전성과 신뢰성이 중요한 안전필수시스템으로, 디지털 계측제어 시스템 개발에 사용되는 상용소프트웨어 들은 검증된 인증 프로세스(COTS SW Dedication)를 거쳐 안전성과 신뢰성이 입증 되어야 한다[1][2][3]. 미국원자력규제위원회(NRC)와 전력연구원(EPRI) 에서는 원자력발전소의 I&C 시스템 개발 혹은 유지보수에 사용하기 위한 상용(COTS: Commercial-Off-The-Shelf) 소프트웨어와 하드웨어의 인증 과정에 대해 가이드라인 (NUREG/CR-6421[1], NP-5652[2], TR-1025243[3] 등)을 제시하고 있다.

IP Core library는 FPGA 개발에서 설계의 편의성 및 효율성을 위해 미리 정의된 기능과 회로의 라이브러리로써, 마찬가지로 원자력 발전소에 사용하기 위해서는 충분한 검증 과정을 거쳐야 한다. 하지만 이러한 IP Core library가 상용 합성도구에서 사용자의 동의나 확인 없이 임의적으로 사용된다면, 상용 합성도구의 dedication 과정에서 이에 따른 영향력을 고려해야 한다.

이에 본 논문에서는 FPGA 기반 디지털 I&C 개발 연구 [4][5]에서 사용된 상용 합성도구인 'Synopsys Synplify Pro'에 대하여 IP Core library 사용 여부에 대해 확인을 통해 'Synplify Pro'의 COTS SW dedication 수행 시 IP Core library 가 미치는 영향에 대해 분석 하였다.

# 2. 배경 지식

# 2.1 상용 소프트웨어의 인증 (COTS SW Dedication)

상용 소프트웨어의 인증에 관련된 표준 및 가이드라인으로 NP-5652[2], TR-106439[6], TR-1025243[3], NUREG/CR-6421[1]이 있다. NP-5652는 대상 상용 품목 (Commercial-grade item)이 기능을 수행하기 위해 보장 되어 야 하는 필수 특성을 기반으로 하여 인증 방법을 선택하는 프 로세스를 제안하고 있다. 그리고 TR-106439는 NP-5652를 기반으로 하여 소프트웨어 및 장비에 대해 제시하고 있다. TR-106439 와 NP-5652는 주로 발전소의 시스템에 직접 사 용되는 상용 품목들에 대해 설명하고 있어 TR-1025243이 추 가적으로 제안 되었다. TR-1025243은 개발 및 분석, 디자인, 소프트웨어 등에 사용되는 (컴퓨터 프로그램)의 dedication 수행 여부에 대해 분류하고 설명하는 기술 보고서 이다. NUREG/CR-6421은 상용 소프트웨어를 대상으로 제안 된 가이드라인으로, 소프트웨어의 안전성 중요도에 따라 카테 고리를 분류 후 개별 인증과정을 적용하고 있다. NUREG/CR-6421에서 사용하고 있는 카테고리는 IEC-61226[8]을 기반으 로 하고 있다.

#### 2.2 IP Core library

IP Core library는FPGA 개발에서 설계의 편의성 및 효율성을 위해 미리 정의된 기능과 회로의 라이브러리로써 일반적으로 FPGA 제공 벤더 별로 제공하고 있으며, 벤더에서 관여하지 않는 3<sup>rd</sup> party 라이브러리 또한 존재 한다. 하지만 라이브

러리를 사용할 때 사용자가 IP Core library의 내부구조 및 동작에 대해 정확히 파악 하기 어렵고, 또한 의도한대로 동작하지 않을 가능성이 있다. 그렇기 때문에 디지털 I&C 시스템 개발에 IP Core library를 사용하고자 하기 위해서는 안전성 및 신뢰성을 위해 반드시 검증된 라이브러리를 사용해야 한다. 이러한 IP Core library 사용여부에 대한 내용은 사용하려는 SW의 dedication 수행 시 반드시 고려 되어야 한다.

## 3. IP Core library 사용 방법 별 영향 및 분석 방법

#### 3.1 IP Core library 사용 방법 별 영향

상용 합성도구는 FPGA 개발에서 RTL design을 Gate-Level design으로 변환하는 합성(Synthesis)을 수행하는 도구로써, 상용 합성도구에서 IP Core library를 사용하여 합성을 수행할 수 있는 경우의 수를 2 가지로 분류하였다.

- 1) 디자인 단계에서 사용한 IP Core library 합성

- 2) 합성도구 임의로 IP Core library를 사용하여 합성

1), 2)번 각각의 경우에 따라 IP Core library의 사용이 상용합성 도구의 dedication에 미치는 영향을 살펴보면 다음과 같다. 1)번 과 같이 디자인 단계에서 사용된 IP Core library의 경우 해당 라이브러리는 디자인에 의존적이고, 디자인 대상의 verification 범위에 포함 된다고 할 수 있다. 그 이유는 디자인에 사용 되어야만 IP Core library를 사용하기 때문이다. 따라서 1)에 해당되는 IP Core library 사용은 합성도구의 COTS SW dedication 수행 시 미치는 영향이 없다고 할 수 있다.

반대로 2)번 과 같은 사용은 합성도구의 기능, 능력과 연관된다고 할 수 있다. 디자인과 관계없이 합성도구의 기능으로 사용하는 것이기 때문이다. 이 경우 상용합성도구의 COTS SW dedication 과정에서 IP Core사용에 대한 고려 및 분석이필요하다. 고려해야 할 점은 합성 과정에서 사용되는 IP Core library의 종류 및 기능과 대상 IP Core들에 대해 V&V 수행 여부 및 결과 확인 또는 사용되는 IP Core들에 대해 특별시험을통한 확인 등 이다.

# 3.2 IP Core library 사용여부 분석 방법

3.1 에서 밝힌 바와 같이 합성 과정에서 합성도구 임의로 IP Core library를 사용할 경우 COTS SW dedication 수행 시확인하고 고려해야 할 점이 존재 한다. 그렇기 때문에 상용합성도구의 dedication 수행 이전에 반드시 IP Core library 사용여부 및 방법 등에 대해 확인이 필요 하다. 이에 본 논문에서는 FPGA 기반 원자력발전소 디지털 계측제어 시스템 개발에 사용된 합성 도구인 'Synopsys Synplify Pro[7]'에 대해 IP Core library 사용 여부 확인과 그에 따른 dedication에 미치는 영향 분석을 수행 하기 위해 2 가지 방법을 이용 하였다.

첫 번째 방법은 라이브러리를 사용한 디자인과, 라이브러리를 사용하지 않고 같은 기능을 하도록 작성된 Verilog 디자인의 합성 결과를 비교 하는 방법이다. 이 방법은 두 결과를 비교함으로써 같은 동작을 수행하는 게이트 합성을 위해 라이브러리를 사용하는지 여부를 확인 하는 방법이다.

두 번째 방법은 실제 사용되는 Verilog 디자인을 합성하고,

그 결과에서 라이브러리를 사용한 부분이 있는지 확인하는 방법이다. 두 번째 방법은 실 사용되는 디자인의 합성 결과에서라이브러리를 사용하는 부분이 있는지 비교 확인하는 방법으로 실험 예제가 아닌 실제 예제에서 사용되는 부분이 있는지확인하기 위해 사용 된다.

다음 장 에서는 'Synplify Pro'의 IP Core library 사용 여부를 확인하기 위해 위에서 설명한 2 가지 방법 수행을 통해 분석한 IP Core library 사용 여부 및 dedication 에 미치는 영향에 대해 설명한다.

# 4. 합성도구의 IP Core library 사용 확인 및 영향 분석

#### 4.1. 라이브러리 사용 유/무 디자인 비교를 통한 확인

3.2 에서 설명한 첫 번째 방법을 이용한 실험을 위해 'Synplify Pro' 사용을 지원하는 통합개발환경인 'Libero SoC'를 통해 라이브러리를 사용한 디자인을 생성하고, 같은 기능의 라이브러리를 사용하지 않은 디자인을 작성 하였다. 실험은 'Libero SoC'의 에서 사용 가능한 디자인 도구의 라이브러리 중 basic block에 해당하는 사칙연산 블록(adder, subtractor, counter, incrementer), 비교블록(Comparator)과 multiplexer를 대상으로 하였다.

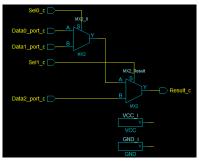

(a) 라이브러리 사용한 합성 결과

(b) 라이브러리 미사용 디자인 합성 결과 그림 1.3 to 1 multiplexer 비교 실험 결과

<그림 1>은 첫 번째 실험 결과 중 3to1 multiplexer에 대해라이브러리를 사용한 디자인과(a), 직접 HDL을 작성 하여라이브러리를 사용하지 않은 디자인(b)의 합성 결과에 대해 각각 나타낸 그림이다. <그림 1> 결과 'Smart Design'의 라이브러리를 사용한 코드는 기본 게이트인 MX2 2개를 사용한 반면 Verilog로 작성된 디자인은 NOR, OR 등의 게이트를 이용하여합성 되었다. 비교를 통해 'Synplify Pro'는 3to1 multiplexer에 대해서 합성 과정에서 'Smart Design'의 라이브러리를 사용하지 않음을 알 수 있다. 다른 라이브러리에 대해서도 같은실험을 수행 하였다.

표 1은 실험 결과에 대한 비교 예제로 위의 3to1 mux와 adder, decoder, incrementer 라이브러리에 대해 비교 한 예제 이다. 각각의 모듈들에 대해서 비교 결과 사용하는 게이트의 종류와 개수가 다름을 확인 할 수 있었다. 다른 모듈들도 마찬가지 4개의 로직과 마찬가지로 사용하는 게이트들의 차이점이 존재함을 확인 하였다.

표 1. 실험 결과 비교 예제

| Logic       | Smart Design(사용) | Verilog(미사용)             |  |

|-------------|------------------|--------------------------|--|

| 3to1 Mux    | 2 개 (2to1 mux 2) | 9 개 (NOT 5, NOR3 1,      |  |

|             |                  | NOR2 2, OR3 1)           |  |

| Decoder     | 6 개 (NOT 2, AND  | 8 개 (NOT 4, NOR 4)       |  |

|             | 3, NOR 1)        |                          |  |

| 4 bit Adder | 11 개 (AND 7,     | 15 개 (AND 6, OR 2, XOR3  |  |

|             | XOR3 3, XOR2 1)  | 3, XOR2 1, NOT 2, NOR 1) |  |

| Incrementer | 6 개 (AND3 1, AND | 9 개 (AND3 1, XOR 3, NOT  |  |

|             | 1, XOR 3, NOT 1) | 3, NOR 2)                |  |

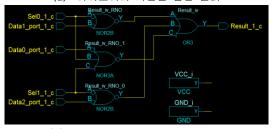

#### 4.2. 실제 예제 비교를 통한 확인

3.2 에서 제시한 두 번째 방법을 이용한 실험을 위해 원자력발전소의 보호 계통(Reactor Protection System)을 구성하는 18개 로직을 이용하였다[4]. 해당 로직은 FPGA 기반 원자력발전소 디지털 계측제어 시스템 개발 연구 중 작성한 원자로보호 계통 로직의 초기 버전으로 총 18개의 로직으로 구성된다. 실험은 18개 로직을 합성한 결과에서 각각의 라이브러리를 합성한 결과가 사용되는지 직접 비교를 통해 수행 하였다. <표 2>는 18개 로직에 대해서 합성 결과와 라이브러리를 통한 합성 결과를 비교하여 라이브러리 사용 여부에 대해 확인한 결과 이다.

표 2.18개 로직 확인 결과

| # 2. 10% I T T C E F |                          |              |                          |  |

|----------------------|--------------------------|--------------|--------------------------|--|

| Logic                | IP Core library<br>사용 여부 | Logic        | IP Core library<br>사용 여부 |  |

| HI_CPRS_NR           | X                        | LO_RC1_FLW   | Х                        |  |

| HI_LOG_POW           | X                        | LO_RC2_FLW   | X                        |  |

| HI_LOG_POW           | X                        | LO_SGL1_WR   | X                        |  |

| HI_PPRS_RPS          | X                        | LO_SGL2_WR   | X                        |  |

| HI_SGL1_RPS          | X                        | LOLO_SGL1_WR | Χ                        |  |

| HI_SGP2_RPS          | X                        | LO_SGL1_WR   | X                        |  |

| HIHI_CPRS_NR         | X                        | LOLO_SGL1_WR | X                        |  |

| LO_DNBR_RPS          | X                        | LO_SGL1_WR   | X                        |  |

| LO_PZR_RPS           | X                        | VAR_OVR_PWR  | X                        |  |

이처럼 여러 예제를 이용해 'Synplify Pro'에 대해 실험한 결과 디자인에 사용되는 여러 가지 IP Core library 및 기본 라이 브러리를 대상 예제에서는 합성 과정에서 임의로 사용하지 않는 것을 확인 할 수 있었다. 예제를 이용한 현재 실험 결과 'Synplify Pro'의 COTS SW dedication 수행 과정에서 IP Core library는 고려 대상이 되지 않는다고 할 수 있다.

# 5. 결론 및 향후 연구

본 논문에서는 상용 합성도구의 IP Core library이 COTS SW dedication에 미치는 영향에 대해 확인하기 위해 라이브러리를 사용/미사용 실험예제를 통한 비교와 실제 사용되는 로직의 초기 버전을 이용한 2 가지 방법의 실험을 통해 실험 하였다. 그 결과 'Synopsys Synplify Pro'는IP Core library를 합성과정에서 임의적으로 사용하지 않는 것을 확인 할 수 있었다. 결과적으로 'Synopsys Synplify Pro'는 dedication 수행 시 IP Core library에 대해 고려할 필요가 없음을 확인 하였다.

향후 일반적인 컴파일러의 optimization 과 같이 합성 도구의 optimization이 IP Core library의 사용과 연관되어 COTS SW dedication에 미치는 영향이 있는지에 대해 확인할 필요가 있으며, 또한 향후 개발 환경에 사용되는 합성 도구 이외의 디자인 도구나 배선 및 배치 도구와 같은 다른 상용 도구들에 대해 IP Core library 사용이 해당 도구들의 dedication에 미치는 영향 및 dedication 수행시 IP Core library에 대해 고려할 점에 대해 연구를 지속적으로 수행할 계획이다.

#### 사 사

본 연구는 한국원자력연구원의 "FPGA-기반 제어기 통합개 발환경을 위한 핵심 소프트웨어 기술 개발" 사업과 "원자력 계측제어 계통 안전 적합성 평가체계" 사업의 지원으로 연구 한 결과 입니다.

## 참 고 문 헌

- [1] Nuclear Regulatory Commission, NUREG/CR-6421 "A Proposed Acceptance Process for Commercial Off-the-Self (COTS) Software in Reactor Applications", 1996.

- [2] Electric Power Research Institute, "Plant Engineering: Guideline for the Acceptance of Commercial-Grade Items in Nuclear Safety-Related Applications", 2013.

- [3] Electronic Power Research Institute, "Plant Engineering: Guideline for the Acceptance of Commercial-Grade Design and Analysis Computer Programs Used in Nuclear Safety-Related Applications (TR-1025243)", 2013

- [4] Jong Gyun Choi, Dong Young Lee, "Development of RPS trip logic based on PLD technology", Nuclear Engineering and Technology, Vol. 44, Num 6. pp 697-708, 2012

- [5] 이동아, 유준범, 최종균, "원자력 발전소의 FPGA 기반 계측제어 시스템을 위한 통합 소프트웨어 개발 환경", 정보과학회지 제 32권 제 12호, p36-43, 2014.

- [6] Electronic Power Research Institute, "Evaluating Commercial Digital Equipment for High-Integrity Applications(TR-106439)", 1996

- [7] Microsemi, www.microsemi.com

- [8] International Electrotechnical Commission, IEC 1226 "Nuclear Power Plants Instrumentation And Control Systems Important For Safety Classification", 1994.