# Advanced Software Engineering Introduction to Model Checking

JUNBEOM YOO KONKUK University

### Text

B. Bérard • M. Bidoit • A. Finkel • F. Laroussinie A. Petit • L. Petrucci • Ph. Schnoebeien with P. McKenzie

# Systems and Software Verification

Model-Checking Techniques and Tools

Springer

DEPENDABLE SOFTWARE LABORATORY

- Automata

- Temporal Logic

- Model Checking

- Property Patterns

# **FORMAL VERIFICATION : BASIC**

# 1. Automata

### 1. Automata

- Model checking consists in verifying some properties of the model of a system.

- Modeling of a system is difficult.

- No universal method exists to model a system.

- Best performed by qualified engineers

- This chapter describes a general model which serves as a basis.

- Organization

- Introductory Examples

- A Few Definitions

- A Printer Manager

- A Few More Variables

- Synchronized Product

- Synchronization with Messaging Passing

- Synchronization by Shared Variables

## **1.1 Introductory Examples**

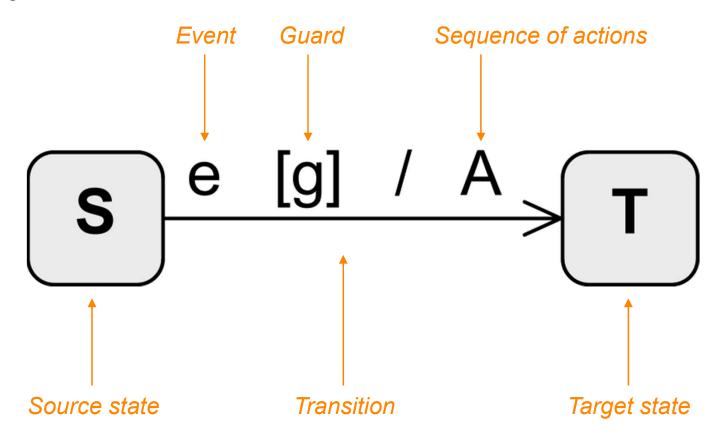

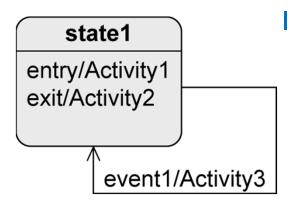

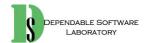

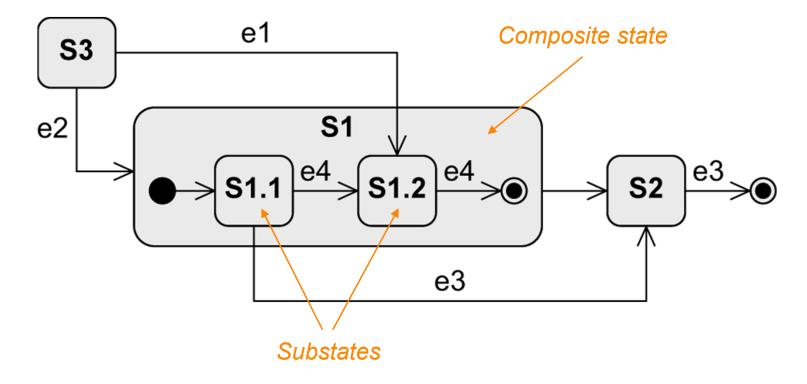

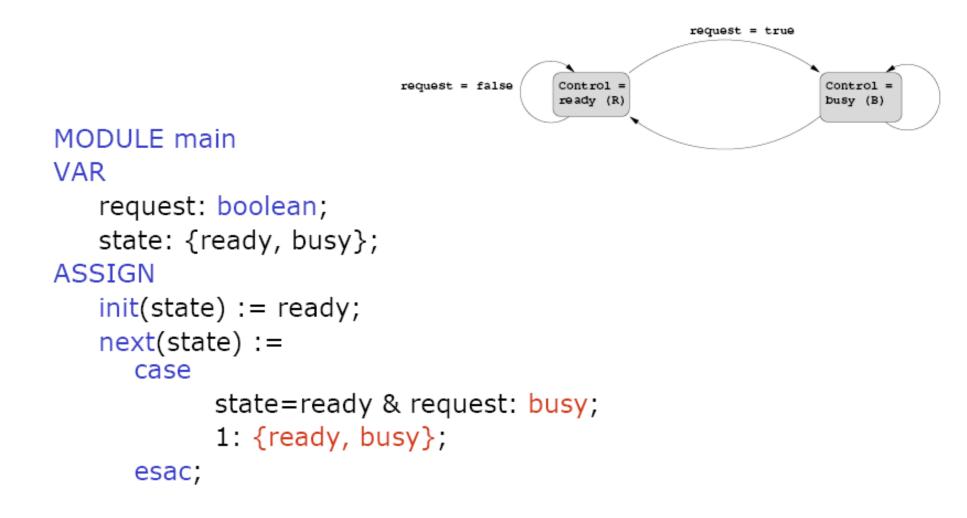

#### • (Finite) Automata

- A machine evolving from one state to another under the action of transitions

- Graphical representation

- Best suited for verification by model checking techniques

An automate model of a digital watch (24x60=1440 states)

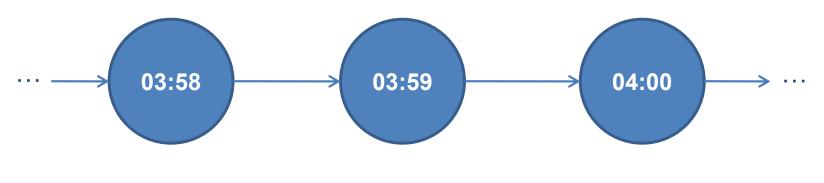

A<sub>c3</sub> : a modulo 3 counter

7

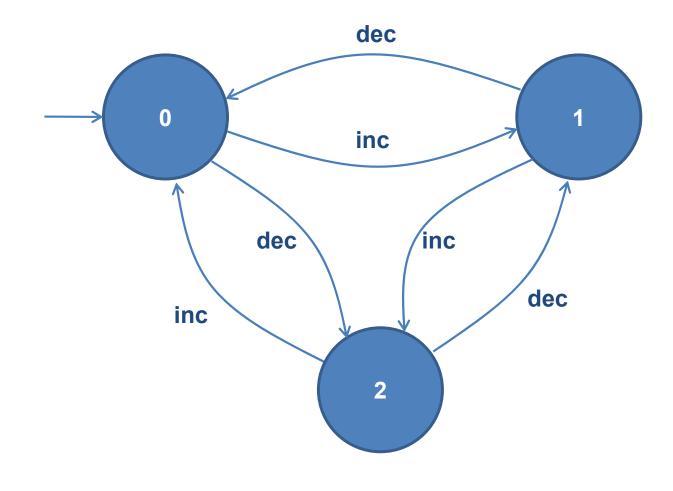

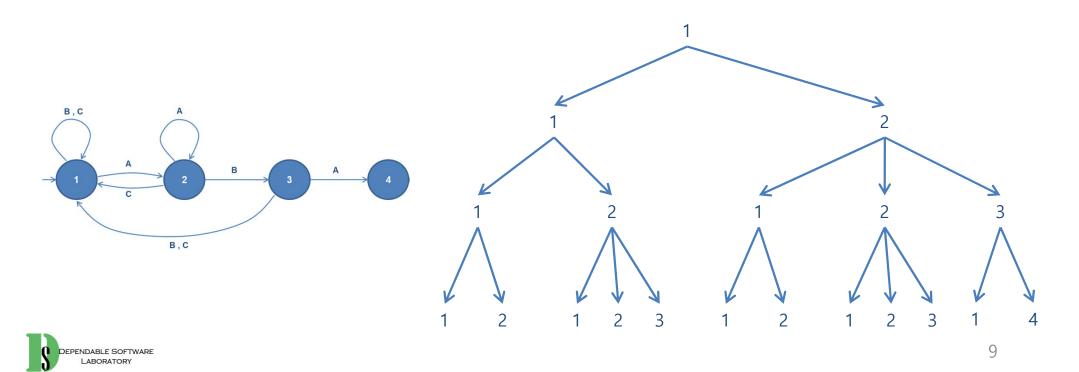

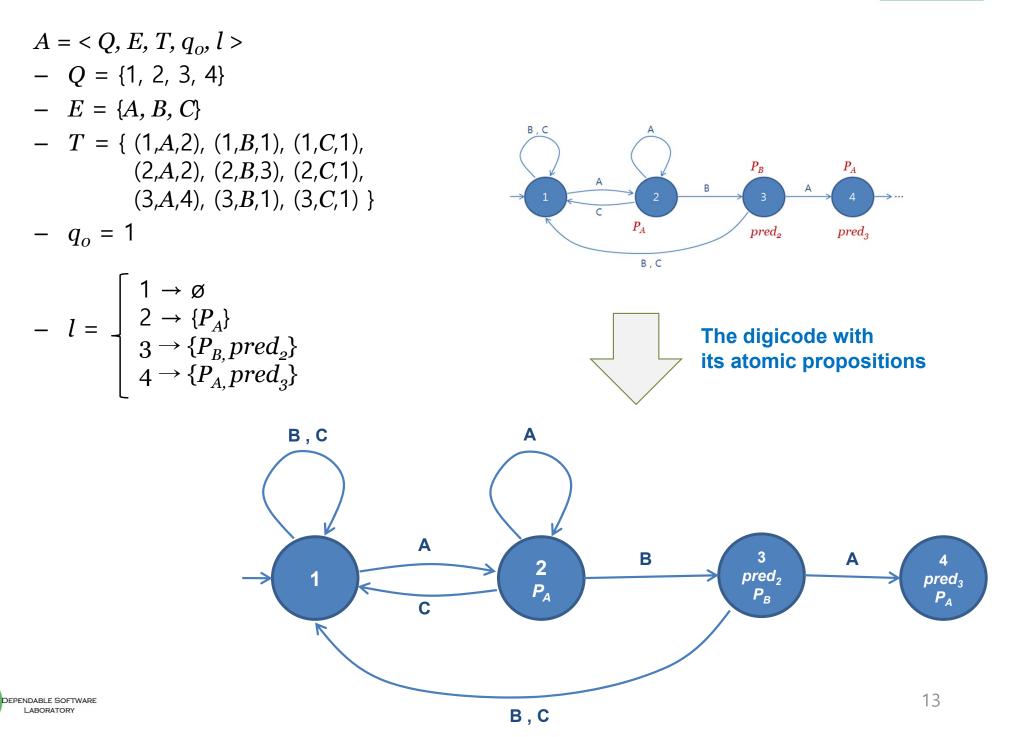

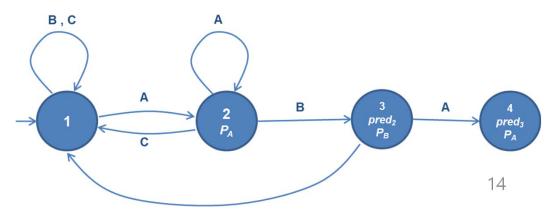

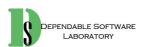

- A digicode door lock example

- Controls the opening of office doors

- The door opens upon the keying in of the correct character sequence, irrespective of any possible incorrect initial attempts.

- Assumptions:

- 3 keys A, B, and C

- Correct key sequence : ABA

- Two fundamental notations

- execution

- A sequence of states describing one possible evolution of the system

- Ex. 1121 , 12234 , 112312234 ← 3 different executions

- execution tree

- A set of all possible executions of the system in the form of a tree

- Ex. 1

```

11, 12

111, 112, 121, 122, 123

1111, 1112, 1121, 1122, 1123, 1211, 1212, 1221, 1222, 1223, 1231,1234

...

```

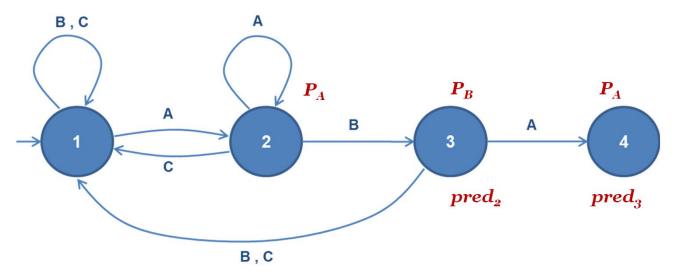

- We now associate each <u>automaton state</u> with a number of <u>elementary</u> <u>properties</u> which we know they are satisfies.

- Since our goal is to verify system model properties.

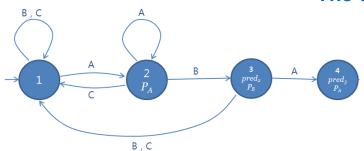

#### • Properties

- Elementary property

- (atomic) Proposition

- Associated with each state

- True or False in a given state

- Complicated property

- Expressed using elementary properties

- Depends on the logic we use

- For example,

- $P_A$ : an A has just been keyed in

- $P_B$ : an *B* has just been keyed in

- $P_C$ : an C has just been keyed in

- $pred_2$ : the proceeding state in an execution is 2

- $pred_3$ : the proceeding state in an execution is 3

- Properties of the system to verify

- 1. If the door opens, then A, B, A were the last three letters keyed in, in that order.

- 2. Keying in any sequence of letters ending in ABA opens the door.

- Let's prove the properties with the propositions

## **1.2 A Few Definition**

- An automaton is a tuple  $A = \langle Q, E, T, q_0, l \rangle$  in which

- Q : a finite set of states

- E : the finite set of transition labels

- $T \subseteq Q \ x \ E \ x \ Q$ : the set of transitions

- $q_o$ : the initial state of the automaton

- -l: the mapping each state with associated sets of properties which hold in it

- *Prop* = {*P*1, *P*2, ... } : a set of elementary propositions

- Formal definitions of automaton's behavior

- a *path* of automaton A :

- A sequence  $\sigma$ , finite or infinite, of transitions which follows each other

- $\text{Ex.3} \xrightarrow{B} 1 \xrightarrow{A} 2 \xrightarrow{A} 2$

- a *length* of a path  $\sigma$ :

- $|\sigma|$

- $\sigma$  's potentially infinite number of transitions:  $|\sigma| \in N \cup \{\omega\}$

- a *partial execution* of A :

- A path starting from the initial state  $q_0$

- Ex.1  $\xrightarrow{A}$  2  $\xrightarrow{A}$  2  $\xrightarrow{B}$  3

- a complete execution of A :

- An execution which is maximal.

- Infinite or deadlock

#### - a reachable state :

- A state is said to be reachable,

- If a state appears in the execution tree of the automaton

- If there exists at least one execution in which it appears

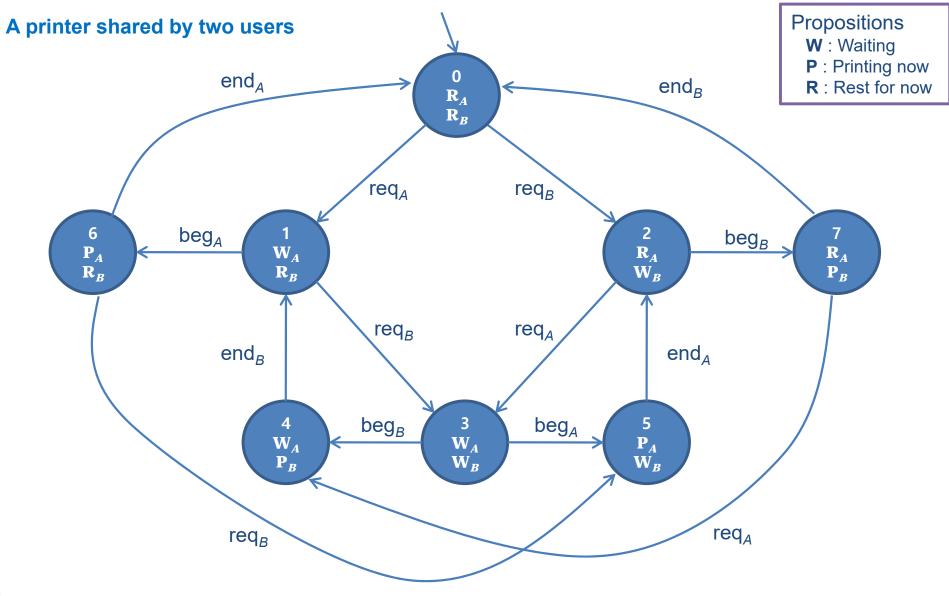

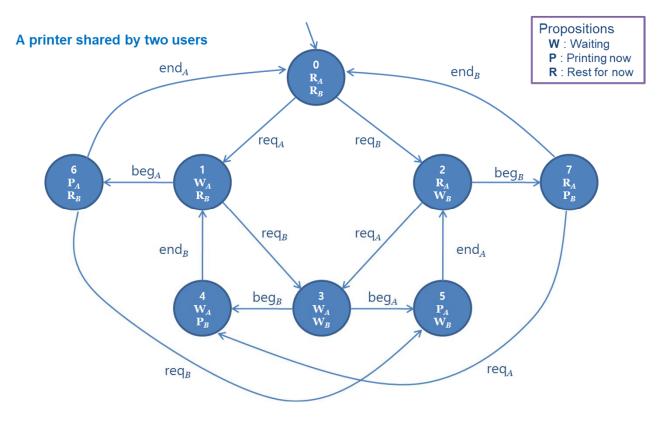

### **1.3 Printer Manager**

$$\begin{split} A &= \langle Q, E, T, q_o, l \rangle \\ &- Q = \{0, 1, 2, 3, 4, 5, 6, 7\} \\ &- E = \{\text{req}_A, \text{req}_B, \text{beg}_{A'}, \text{beg}_B, \text{end}_{A'}, \text{end}_B\} \\ &- T = \{ (0, \text{req}_{A'}1), (0, \text{req}_{B'}2), (1, \text{req}_B, 3), (1, \text{beg}_A, 6), (2, \text{req}_A, 3), \\ (2, \text{beg}_B, 7), (3, \text{beg}_A, 5), (3, \text{beg}_B, 4), (4, \text{end}_B, 1), (5, \text{end}_A, 2), \\ (6, \text{end}_A, 0), (6, \text{req}_B, 5), (7, \text{end}_B, 0), (7, \text{req}_A, 4) \} \\ &- q_o = 0 \\ \\ &- l = \begin{cases} 0 \rightarrow \{R_{A'}, R_B\}, & 1 \rightarrow \{W_{A'}, R_B\} \\ 2 \rightarrow \{R_{A'}, W_B\}, & 3 \rightarrow \{W_{A'}, W_B\} \\ 4 \rightarrow \{W_{A'}, P_B\}, & 5 \rightarrow \{P_{A'}, W_B\} \\ 6 \rightarrow \{P_{A'}, R_B\}, & 7 \rightarrow \{R_{A'}, P_B\} \end{cases} \end{split}$$

- **Properties** of the printer manager to verify

- 1. We would undoubtedly wish to prove that any printing operation is preceded by a print request.

- In any execution, any state in which P<sub>A</sub> holds is preceded by a state in which the proposition W<sub>A</sub> holds.

- 2. Similarly, we would like to check that any print request is ultimately satisfied.  $(\rightarrow \text{ fairness property})$

- In any execution, any state in which W<sub>A</sub> holds is followed by a state in which the proposition P<sub>A</sub> holds.

- Model checking techniques allow us to prove automatically

- Property 1 is TRUE.

- Property 2 is FALSE,

- A counterexample : 0 1 3 4 1 3 4 1 3 4 1 3 4 1 ...

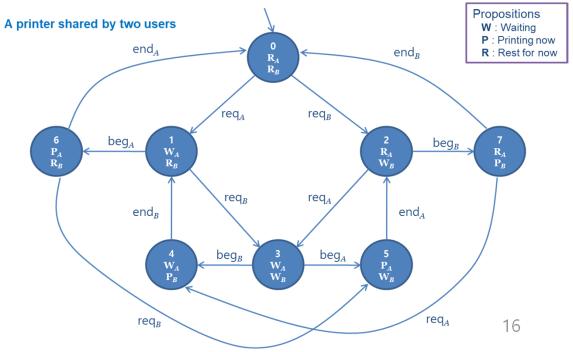

### **1.4 Few More Variables**

- It is often convenient to let automata manipulate state variables.

- Control : states + transitions

- Data : variables (assumes finite number of values)

- An automaton interacts with variables in two ways:

- Assignments

- Guards (guarding conditions)

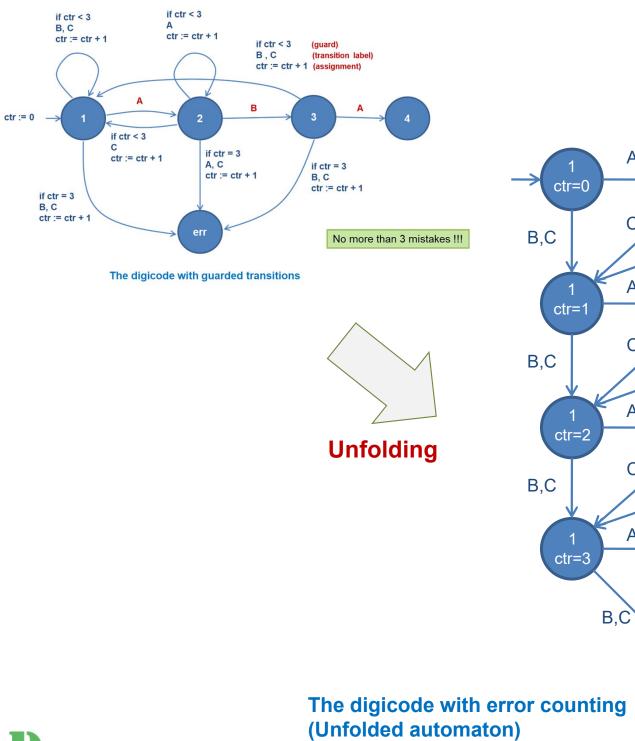

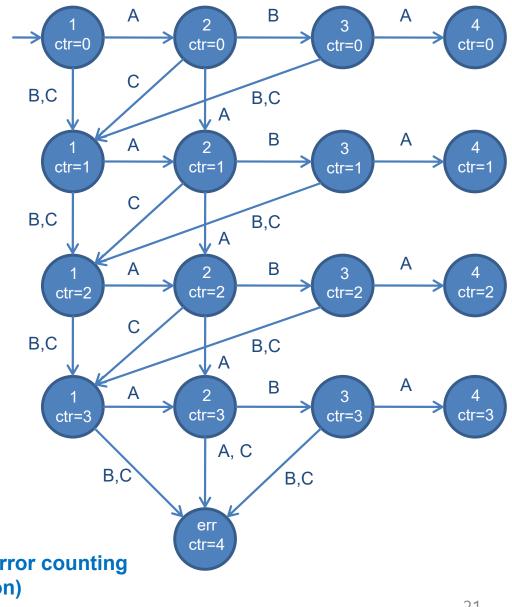

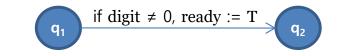

The digicode with guarded transitions

- It is often necessary, in order to apply model checking methods,

- to *unfold* the behaviors of an automaton with variables

- into a state graph

- in which the possible transitions appear, and the configurations are clear marked.

- Unfolded automaton = Transition system

- has <u>global states</u>

- transitions are <u>no longer guarded</u>

- <u>no assignments</u> on the transitions

KU KONKUK UNIVERSITY

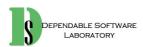

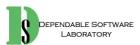

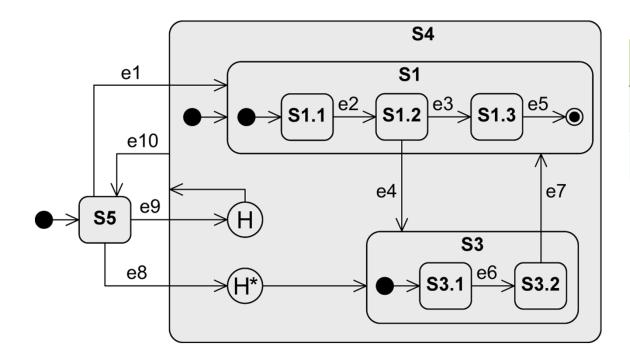

### **1.5 Synchronized Product**

- Real-life programs or systems are often composed of **modules** or subsystems.

- − Modules/Components  $\rightarrow$  (composition)  $\rightarrow$  Overall system

- Component automata  $\rightarrow$  (synchronization)  $\rightarrow$  Global automaton

- Automata for an overall system often has so many global states.

- Impossible to construct it directly (State explosion problem)

- We need to construct it with small component automata.

- Two composition ways

- With synchronization (= Synchronized product)

- Without synchronization (= Cartesian product)

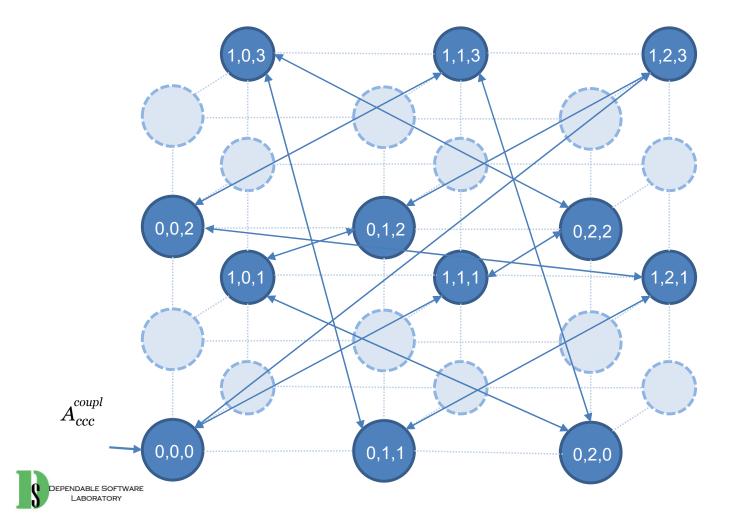

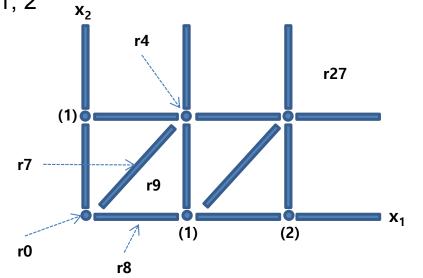

- An example without synchronization ۲

- A system made up of three counters (modulo 2, 3, 4)

- They do not interact with each other. —

LABORATORY

Global automaton = Cartesian product of three independent automata

- An example <u>with synchronization</u>

- There are a number of ways depending on the nature of the problem.

- Ex. Allowing only "inc, inc, inc" and "dec, dec, dec" (24\*2=48 transitions)

- Ex. Allowing updates in only one counter at a time (24\*3\*2=144 transitions)

#### Synchronized product

- A way to formally express synchronizing options

- Synchronized product = Component automata + Synchronized set

- $A_1 \times A_2 \times \ldots \times A_n$  : Component automata

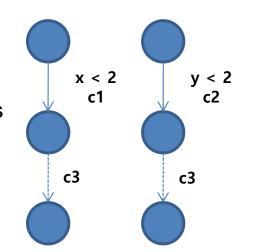

$$- A = \langle Q, E, T, q_{0}, I \rangle \\

- Q = Q_{1} \times Q_{2} \times ... \times Q_{n} \\

- E = \prod_{1 \le i \le n} (E_{i} \cup \{-\}) \\

- T = \left\{ \begin{array}{l} ((q_{1}, ..., q_{n}), (e_{1}, ..., e_{n}), (q'_{1}, ..., q'_{n})) \mid \text{ for all } i, \\

(e_{i} = `-` \text{ and } q'_{i} = q_{i}) \text{ or } (e_{i} \neq `-` \text{ and } (q_{i}, e_{i}, q'_{i}) \in T_{i}) \end{array} \right\} \\

- q_{0} = (q_{0,1}, ..., q_{0,n}) \\

- I((q_{1}, ..., q_{n})) = \bigcup_{1 \le i \le n} l_{i}(q_{i})$$

- Sync  $\subseteq \prod_{1 \le i \le n} (E_i \cup \{-\})$  : Synchronized set

#### • An example <u>with synchronization</u>

- Allowing only "inc, inc, inc" and "dec, dec, dec" (24\*2=48 transitions)

→ Strongly coupled version of modular counters

- Sync = { (inc, inc, inc), (dec, dec, dec) }

$$- T = \begin{cases} ((q_1, \dots, q_n), (e_1, \dots, e_n), (q'_1, \dots, q'_n)) \mid (e_1, \dots, e_n) \in Sync \\ (e_i = `-` and q'_i = q_i) \text{ or } (e_i \neq `-` and (q_i, e_i, q'_i) \in T_i) \end{cases}$$

12 states

24 transitions (inc, inc, inc) (dec, dec, dec)

#### Reachable states

Reachability depends on the synchronization constraints

#### Reachability graph

- Obtained by deleting non-reachable states

- Many tools to construct R.G. of synchronized product of automata

- Reachability is a difficult problem.

- State explosion problem

## **1.6 Synchronization with Message Passing**

- Message passing framework

- A special case of synchronized product

- **!m** : Emitting a message

- **?m** : Reception of the message

- Only the transition in which !m and ?m pairs are executed simultaneously is permitted.

- Synchronous communication

- Control/command system

- Asynchronous communication

- Communication protocol (using channel/buffer)

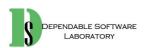

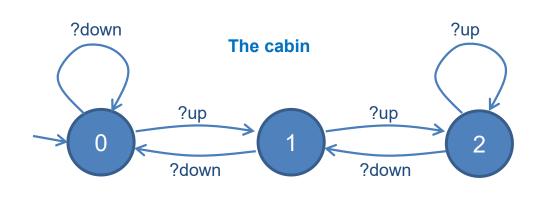

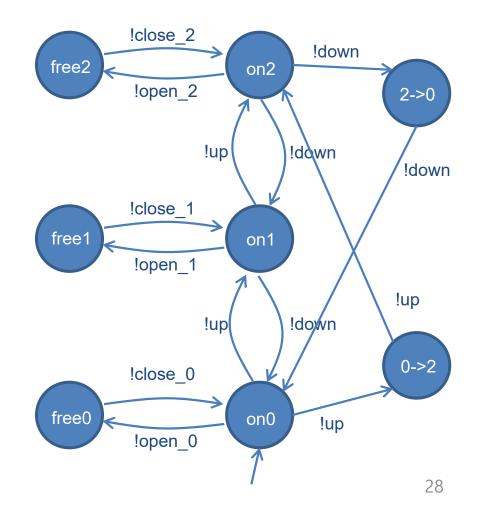

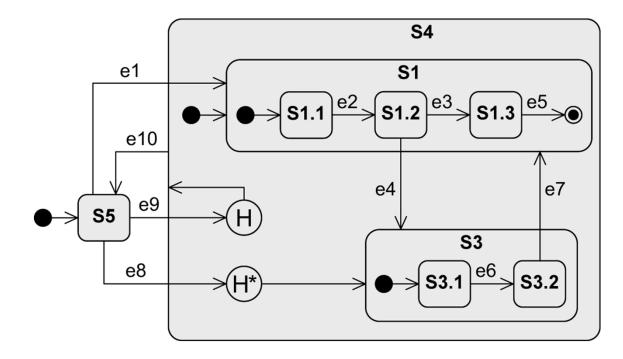

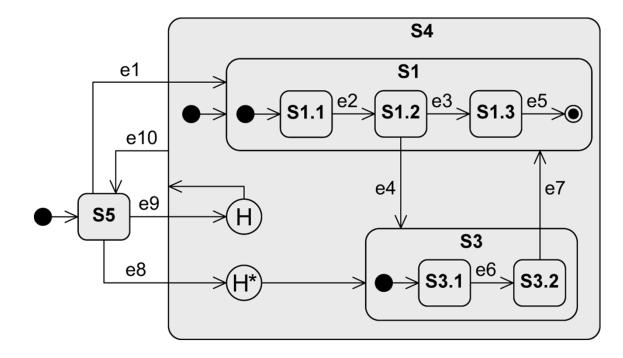

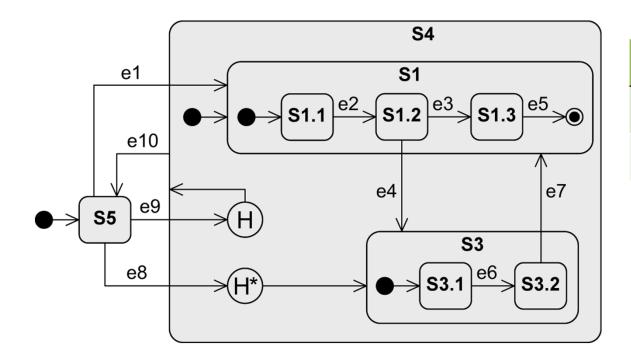

#### • Smallish elevator

- Synchronous communication (message passing)

- One cabin

- Three doors (one per floor)

- One controller

- No request from the three floors

The *i*<sup>th</sup> door

- An automaton for the smallish elevator example

- Obtained as the synchronized product of the 5 automata

- (door 0, door 1, door 2, cabin, controller)

```

- Sync = { (?open_0, -, -, -, !open_0), (?close_0, -, -, -, !close_0),

(-, ?open_1, -, -, !open_1), (-, ?close_1, -, -, !close_1),

(-, -, ?open_2, -, !open_2), (-, -, ?close_2, -, !clsoe_2),

(-, -, -, ?down, !down), (-, -, -, ?up, !up) }

```

#### • **Properties** to check

- (P1) The door on a given floor cannot open while the cabin is on a different floor.

- (P2) The cabin cannot move while one of the door is open.

- Model checker

- Can build the synchronized product of the 5 automata.

- Can check automatically whether properties hold or not.

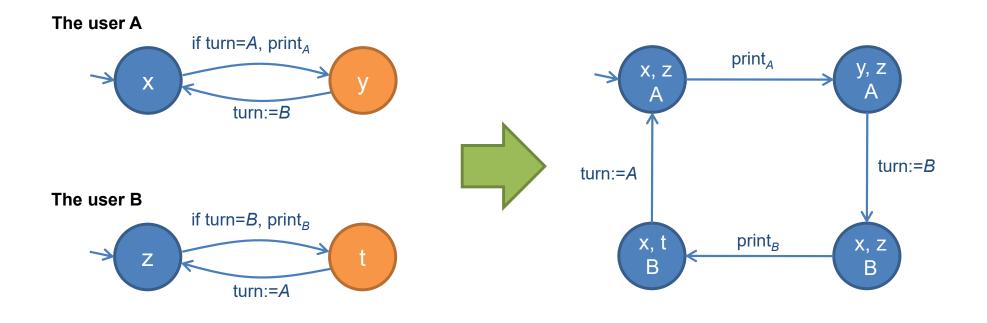

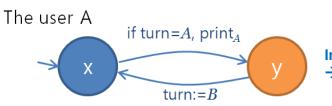

## **1.7 Synchronization by Shared Variables**

- Another way to have components communicate with each other

- Share a certain number of variables

- Allow variables to be **shared** by several automata

- Ex. The printer manager in Chapter 1.3

- Problem: Fairness property is not satisfied.

- The printer manager synchronized with a shared variable

- Shared variable: turn

- Fairness property: "Any print request is ultimately satisfied."

- No state of the form (y, t, -) is reachable.

- TRUE in the model

- But this model forbids either user from printing twice in a row.

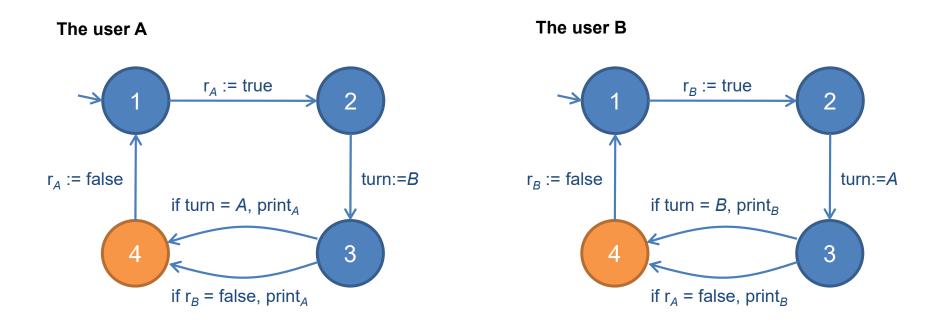

- Printer manager : A complete version with 3 variables [by Peterson]

- $\mathbf{r}_{A}$ : a request from user A

- **r**<sub>B</sub> : a request from user B

- turn : to settle conflicts

- Satisfies all our properties.

$$A_{A_{XB}} = \langle Q, E, T, q_{O}, l \rangle$$

-

$$Q = A \times B \times r_{A} \times r_{B} \times turn$$

$$4 \times 4 \times 2 \times 2 \times 2 = 128 \text{ states (only 128 reachable states)}$$

# 2. Temporal Logic

## 2. Temporal Logic

- Motivation:

- The elevator example includes two properties

- "Any elevator request must ultimately be satisfied."

- "The elevator never traverses a floor for which a request is pending without satisfying this request."

- $\rightarrow$  Dynamic behavior

- In a first order logic,

•

$$\forall t, \forall n (app(n, t) \Rightarrow \exists t' > t : serv(n, t'))$$

•  $\forall t, \forall t' > t, \forall n, \begin{bmatrix} (app(n, t) \land H(t') \neq n \land \exists t_{trav} : \\ t \leq t_{trav} \leq t' \land H(t_{trav}) = n) \\ \Rightarrow (\exists t_{serv} : t \leq t_{serv} \leq t' \land serv(n, t_{serv})) \end{bmatrix}$

- But, the above notation (mathematics) is quite cumbersome.

- **Temporal Logic** is a different formalism, better suited for our situation.

## 2. Temporal Logic

#### Temporal Logic

- A form of logic specifically tailored for statements and reasoning

- involving the notion of order in time

- Compared with the mathematical formulas

- clearer and simpler

- immediately ready for use (linguistic similarity of operators)

- formal semantics (specification language tools)

- Organization

- The Language of Temporal Logic

- The Formal Syntax of Temporal Logic

- The Semantics of Temporal Logic

- PLTL and CTL: Two Temporal Logics

- The Expressivity of CTL\*

# 2.1 The Language of Temporal Logic

- CTL\*

- serves to formally state the properties concerned with the execution of a system

- variants (CTL, PLTL, LTL)

- 6 characteristics

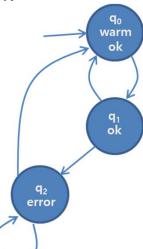

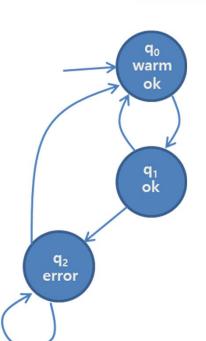

#### **1. Atomic Propositions**

- warm, ok, error

#### 2. Proposition Formula

- using Boolean combinators

- true, false,  $\neg$ ,  $\lor$ ,  $\land$ ,  $\Rightarrow$  (if then),  $\Leftrightarrow$  (if and only if)

q<sub>0</sub> warm ok q<sub>1</sub> ok q<sub>2</sub> error

error ⇒ ¬ warm

(if error then not warm)

$\begin{aligned} \sigma_1 &: (q_0: warm, ok) \rightarrow (q_1: ok) \rightarrow (q_0: warm, ok) \rightarrow (q_1: ok) \rightarrow ... \\ \sigma_2 &: (q_0: warm, ok) \rightarrow (q_1: ok) \rightarrow (q_2: error) \rightarrow (q_0: warm, ok) \rightarrow (q_1: ok) \rightarrow ... \\ \sigma_3 &: (q_0: warm, ok) \rightarrow (q_1: ok) \rightarrow (q_2: error) \rightarrow (q_2: error) \rightarrow (q_2: error) \rightarrow ... \end{aligned}$

#### 3. Temporal combinators

- about the sequencing of states along an execution

- X : next state

- F : a future state

- $\sigma_2 : (q_0: warm, ok) \rightarrow (q_1: ok) \rightarrow (q_2: error) \rightarrow (q_0: warm, ok) \rightarrow (q_1: ok) \rightarrow \dots$

- G : all the future states

- X P : the next state satisfies P

- F P : a future state satisfies P without specifying which state

→ P will hold some day (at least once)

- G P : all future states will satisfy P

→ P will always be

- $alert \Rightarrow F halt$  : if we are currently in a state of *alert*, then we will later be in a *halt* state.

- G (*alert* ⇒ F *halt*) : at any time, a state of *alert* will necessarily be followed by a *halt* state later.

- G (warm  $\Rightarrow$  F  $\neg$ warm ) : true

- G (warm  $\Rightarrow$  X  $\neg$ warm ) : true

- G is the dual of F

- G  $\phi \equiv \neg F \neg \phi$

#### 4. Arbitrary nesting of temporal combinators

- giving temporal logic its power and strength

- GF  $\phi$ : always there will some day be a state such that  $\phi$ ,  $\phi$  is satisfied infinitely often along the execution considered

- FG  $\phi$  : all the time from a certain time onward, at each time instant, possibly excluding a finite number of instants

- GF warm  $\lor$  FG error

#### 5. U combinator

• for until

٠

- $\phi_1 \cup \phi_2 : \phi_1$  is verified until  $\phi_2$  is verified  $\phi_2$  will be verified some day, and  $\phi_1$  will hold in the meantime

- G  $(alert \Rightarrow (alarm \cup halt))$ : starting from a state of alert, the alarm remains activated until the halt state is eventually and inexorably reached.

- F  $\phi$  = true U  $\phi$

- $\phi_1 W \phi_2 \equiv (\phi_1 U \phi_2) \vee G \phi_1$  : weak until

#### 6. Path quantifier

- A  $\phi$  : all the executions out of the current state satisfy property  $\phi$

- E  $\phi$  : from the current state, there exists an execution satisfying  $\phi$

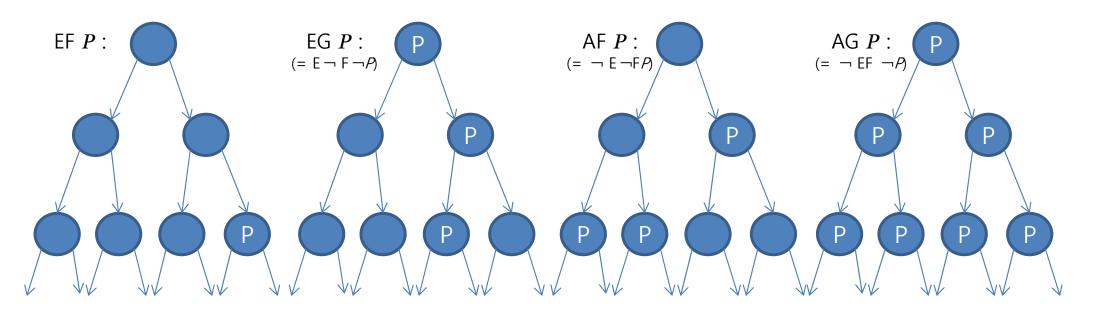

- EF *P* : it is possible (by following a suitable execution) to have *P* some day

- EG P: there exists an execution along which P always holds

- AF *P* : we will necessarily have *P* some day (regardless of the chosen execution)

- AG P: always true

# 2.2 Formal Syntax of Temporal Logic

- Abstract grammar

- needs parentheses, operator priority, specific set of atomic propositions, etc.

- Most model checkers use a fragment of CTL\* CTL or LTL.

$$- \phi, \Psi ::= P1 | P2 | ...| \neg \phi | \phi \land \Psi | \phi \Rightarrow \Psi | ...| X\phi | F\phi | G\phi | \phi U\Psi | ...| E\phi | A\phi$$

(atomic proposition)(boolean combinators)(temporal combinators)(path quantifiers)

# **2.3 The Semantics of Temporal Logic**

#### Kripke structure

- Name of the models of temporal logic

- Propositions labeling the states are important in CTL\*

- Transition labels (*E*) are neglected.  $A = \langle Q, T, q_o, l \rangle$ ,  $T \subseteq Q \times Q$

#### Satisfaction

- A, $\sigma$ ,i  $\ddagger \phi$

- "at time *i* of the execution  $\sigma$ ,  $\phi$  is true."

- where  $\sigma$  is an execution of A, which not required to start at the initial state

- *A* is often omitted.

- $\sigma, i \not\models \phi$  :  $\phi$  is satisfied at time *i* of  $\sigma$

- $\sigma, i \not\models \phi$  :  $\phi$  is not satisfied at time *i* of  $\sigma$

- $A \not\models \phi$  iff  $\sigma$ ,  $0 \not\models \phi$  for every execution of  $\sigma$  of A

- "the automaton A satisfies  $\phi$ "

- $A \not\models \phi \neq A \not\models \neg \phi$

- $\sigma,i \not\models \phi = \sigma,i \not\models \neg \phi$

KU KONKUK UNIVERSITY

$$\begin{array}{ll} \sigma,i\models P & \text{iff } P\in l(\sigma(i)),\\ \sigma,i\models\neg\phi & \text{iff it is not true that } \sigma,i\models\phi,\\ \sigma,i\models\phi\wedge\psi & \text{iff } \sigma,i\models\phi \text{ and } \sigma,i+1\models\phi,\\ \sigma,i\models F\phi & \text{iff there exists } j \text{ such that } i\leq j\leq |\sigma| \text{ and } \sigma,j\models\phi,\\ \sigma,i\models G\phi & \text{iff for all } j \text{ such that } i\leq j\leq |\sigma|, \text{ we have } \sigma,j\models\phi,\\ \sigma,i\models\phi\cup\psi & \text{iff there exists } j, i\leq j\leq |\sigma| \text{ such that } \sigma,j\models\psi, \text{ and}\\ \text{for all } k \text{ such that } i\leq k< j, \text{ we have } \sigma,k\models\phi,\\ \sigma,i\models A\phi & \text{iff for all } \sigma' \text{ such that } \sigma(0)\dots\sigma(i)=\sigma'(0)\dots\sigma'(i) \text{ and}\\ \sigma',i\models\phi.\\ \end{array}$$

#### Semantics of CTL\*

#### CTL\*

- Time is discrete.

- Nothing exists between i and i + 1.

- The instants are the points along the executions

# 2.4 PLTL and CTL: Two Temporal Logics

- Two most commonly used temporal logics in model checking tools

- PLTL (Propositional Linear Temporal Logic)

- CTL (Computational Tree Logic)

- fragments of CTL\*

#### • PLTL

- No path quantifiers (A and E)

- Linear time logic  $\rightarrow$  Path formula

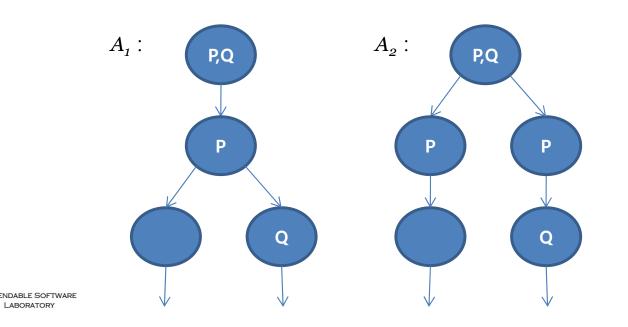

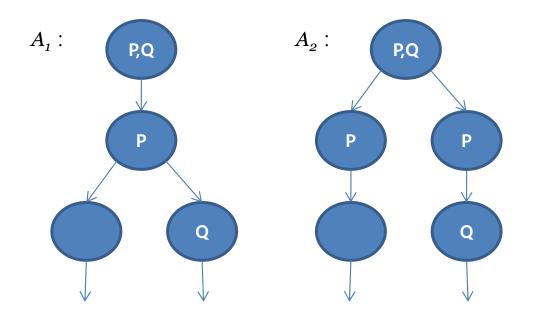

- Ex. PLTL cannot distinguish  $A_1$  from  $A_2$

Execution 1 : {P, Q} . {P}. {-} Execution 2 : {P, Q} . {P} . {Q}

#### • CTL

- Temporal combinators (X, F, U) should be under the immediate scope of path quantifier (A, E)

- EX , AX , EU , AU , EF , EG , AG , AF , ...

- State formulas

- Truth only depends on the current state and the automaton regions made reachable by it

- Not depending on a current execution

- $q \not\models \phi$  :  $\phi$  is satisfied in state q

- CTL can distinguish automata  $A_1$  and  $A_2$

# $egin{aligned} &A_{1}\!, q_{o} & \end{aligned} & \operatorname{\mathsf{AX}}\left(\operatorname{\mathsf{EX}} Q \wedge \operatorname{\mathsf{EX}} \neg Q ight) \ &A_{2}\!, q'_{o} & \end{aligned} & \operatorname{\mathsf{AX}}\left(\operatorname{\mathsf{EX}} Q \wedge \operatorname{\mathsf{EX}} \neg Q ight) \end{aligned}$

- Potential reachability : AG EF P

- Do not allow to express very rich properties along the paths.

- Which to choose CTL or PLTL?

- To state some properties : PLTL

- To perform exhaustive verification of a system : CTL

- For both purposes : CTL\*

- Less popular

- More complicated than PLTL

- CTL + Fairness properties : FCTL

- If we use model checking tools, we have no choice

- SMV : CTL / PLTL

- SPIN : PLTL

- VIS : CTL / PLTL

- No model checking tool for CTL\*

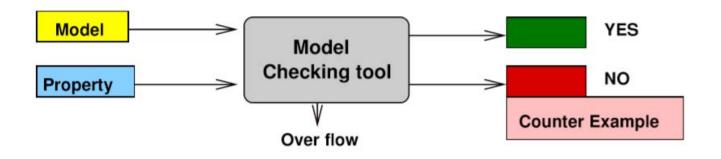

# 3. Model Checking

# 3. Model Checking

- Motivation:

- Describe the principles underlying the algorithms used for model checking

- The algorithm to find out whether a given automaton satisfies a given temporal formula

- Different algorithms for CTL and PLTL

- Organization

- Model Checking CTL

- Model Checking PLTL

- The State Explosion Problem

# **3.1 Model Checking CTL**

- Model checking algorithm for CTL

- Developed in 1980s

- Runs in time linear in each of its components (automaton and CTL formula)

- Relies on the fact that CTL can only express state formulas

- Basic principles

- procedure <u>marking</u>

- Starting from a CTL formula  $\phi$

- Mark for each state q of the automaton and for each sub-formula  $\psi$  of  $\phi$ ,

- Whether  $\psi$  is satisfied in state q

- Complexity of the algorithm

- Model checking " does  $A,q_o \nmid \Phi$  ? " for a CTL formula  $\Phi$

- can be solved in time O(  $|A| \times |\Phi|$  )

- O(|A|): for marking the automaton

- $O(|\Phi|)$ : for each sub-formula in  $\Phi$

- Linear!!!

```

procedure marking(phi)

case 1: phi = P

for all q in Q, if P in 1(q) then do q.phi := true,

else do q.phi := false.

case 2: phi = not psi

do marking(psi);

for all q in Q, do q.phi := not(q.psi).

case 3: phi = psi1 /\ psi2

do marking(psi1); marking(psi2);

for all q in Q, do q.phi := and(q.psi1, q.psi2).

case 4: phi = EX psi

do marking(psi);

case 6: phi = A psi1 U psi2

do marking(psi1); marking(psi2);

/* initialisation */

for all q in Q, do q.phi := false;

/* L: states to be processed */

L := \{\}

for all (q,q') in T, if q'.psi = true then do q.phi := true.

for all q in Q,

q.nb := degree(q); q.phi := false;

/* initialisation */

case 5: phi = E psi1 U psi2

for all q in Q, if q.psi2 = true then do L := L + { q };

do marking(psi1); marking(psi2);

while L nonempty {

for all q in Q,

/* must mark q */

draw q from L;

q.phi := false; q.seenbefore := false;/* initialisation */

L := L - \{q\};

L := \{\};

/* L: states to be processed */

q.phi := true;

for all q in Q, if q.psi2 = true then do L := L + { q };

/* q' is a predecessor of q */

for all (q',q) in T {

while L nonempty {

/* decrement */

q'.nb := q'.nb - 1;

/* must mark q */

draw q from L;

if (q'.nb = 0) and (q'.psi1 = true) and (q'.phi = false)

L := L - \{q\};

then do L := L + \{q'\};

q.phi := true;

}

for all (q',q) in T { /* q' is a predecessor of q */

if q'.seenbefore = false then do {

q'.seenbefore := true;

if q'.psi1 = true then do L := L + \{q'\};

}

}

}

```

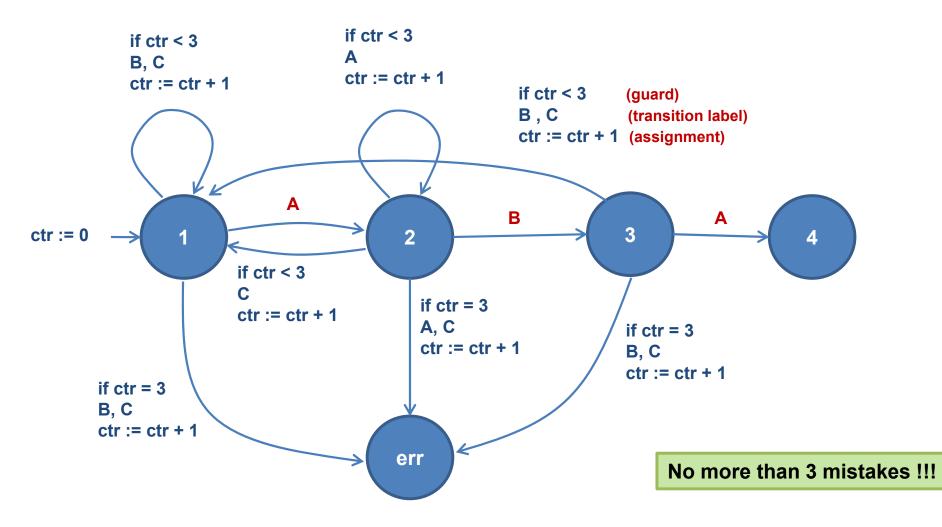

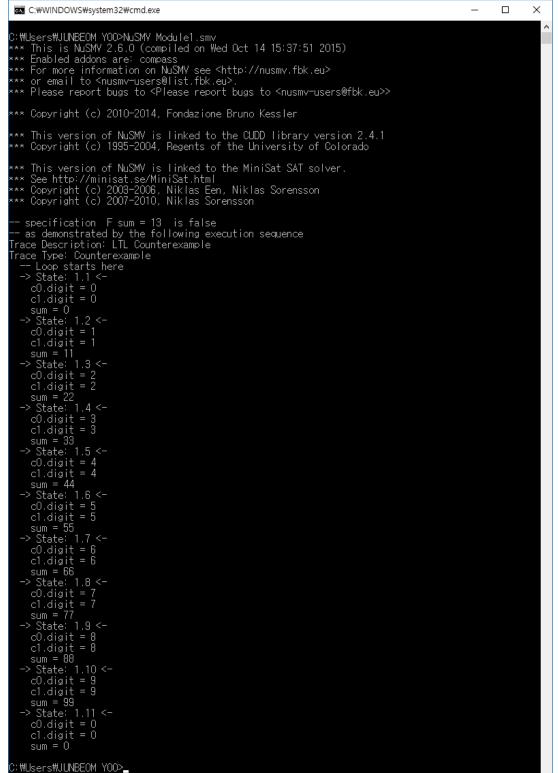

# **3.2 Model Checking PLTL**

- Model checking algorithm for PLTL

- Developed in 1980s, but too technical to cover in this course

- Not possible to rely on marking the automaton states, since PLTL uses path formulas.

- A finite automaton will generally give rise to infinitely many different executions, themselves often infinite in length.

- Hence, PLTL uses a <u>language theory</u> :  $\omega$ -regular expression

- An extension of a regular expression

- "\*" : an arbitrary but finite number of repetitions

- (a b\* + c)\*

- "ω": an infinite number of repetitions

- Basic principle

- Model checking " does  $A \nmid \phi$  ? " for a PLTL formula  $\phi$

- Reduces to a " Are all the execution of A described by  $\varepsilon_{\phi}$ ?"

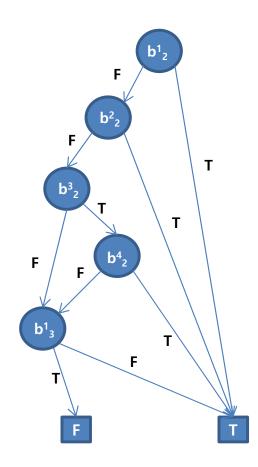

- A PLTL model checker construct an automaton  $B_{\neg\phi}$  (recognizing executions which do not satisfy  $\phi$ )

- Strongly synchronize A and  $B_{\neg\phi} \rightarrow A \otimes B_{\neg\phi}$

- Finally reduces to " is the language recognized by  $A \otimes B_{\neg\phi}$  empty ?"

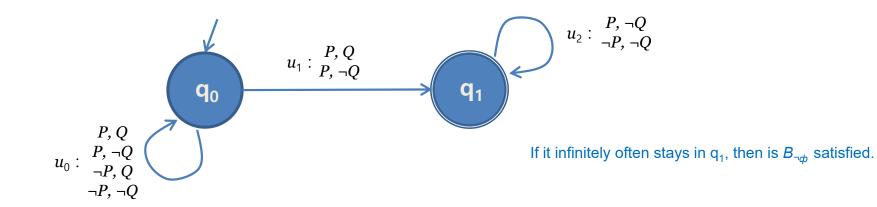

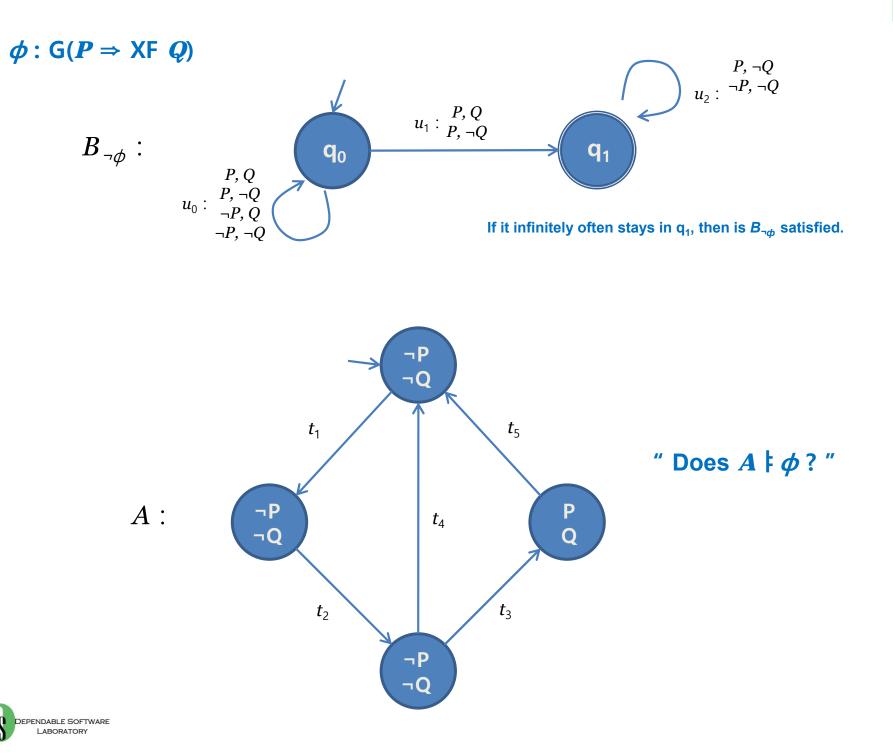

- A simple example

- $-\phi$ : G(P  $\Rightarrow$  XF Q) : Any occurrence of P must be followed (later) by an occurrence of Q

- $B_{\neg\phi}$  : There exists an occurrence of *P* after which we will never again encounter Q

$A \otimes B_{\neg \phi}$  :  $t_5 \otimes u_1$ ¬Ρ ٦Q ¬P  $t_1 \otimes u_2$ ¬Q  $t_5 \otimes u_0$  $t_1 \otimes u_0$ ¬P Ρ  $t_4 \otimes u_2$ ¬Q Q ¬P Ρ  $t_4 \otimes u_0$ Q  $t_2 \otimes u_2$ ¬Q  $t_3 \otimes u_2$ ¬P  $t_2 \otimes u_0$  $t_3 \otimes u_0$ **¬O** ¬P ٦Q

There are behaviors of A accepted by  $A \otimes B_{\neg \phi}$

→ The language recognized by  $A \otimes B_{\neg \phi}$  is nonempty. →  $A \not\models \phi$

- Construction of  $B_{\neg\phi}$

- Very difficult technically

- Automaton  $B_{\neg\phi}$  must in general be able to recognize infinite words

- → Büchi automata

- Complexity of the algorithm

- $B_{\neg\phi}$  has size O(2<sup>| $\phi$ |</sup>) in the worst case

- $A \otimes B_{\neg \phi}$  has size  $O(|A| \times |B_{\neg \phi}|)$

- If  $A \otimes B_{\neg \phi}$  fits in computer memory, we can determine it in time  $O(|A| \times |B_{\neg \phi}|)$

- Model checking "does A,  $q_0 \nmid \phi$ ?" for a PLTL formula  $\phi$  can be done in time  $O(|A| \times 2^{|\phi|})$

#### Reachability analysis

- We can say that  $B_{\neg\phi}$  observes the behavior of A when the two automata are synchronized.

- Observable automata = formal specification of the desired property

- UPPAAL

- SPIN

# **3.3 The State Explosion Problem**

#### State explosion problem

- The main obstacle encountered by model checking algorithms

- The algorithms rely on explicit construction of the automaton A

- Traversal and marking (in case of CTL)

- Synchronization with  $B \neg \phi$  and seeking of reachable states and loops (in case of PLTL)

- In practice, the number of states of A is quickly very large.

- If we use values that are not priori bounded (integers, a waiting queue, etc.), we cannot even apply it.

- Explicit model checking  $\rightarrow$  Symbolic model checking (Chapter 4)

### **Patterns of Temporal Properties**

- Writing the temporal logic formulas expressing desired system properties is important but difficult.

- No silver bullet

- No automatic generation

- 4 classification (categories/patterns) according to verification goals

- Reachability property

- Some particular situation can be reached.

- Safety property

- Under certain condition, something never occurs.

- Liveness property

- Under certain condition, something will ultimately occur.

- Fairness property

- Under certain condition, something will (or not) occur infinitely often.

#### Deadlock freeness

# 4. Properties

# **Reachability Properties**

# 6. Reachability Properties

- Reachability property

- Some particular situation can be reached.

- Examples:

- (R1) "We can obtain n<0 "

- (R2) " We can enter a critical section " ← simple

- (R3) "We cannot have n<0 "

- (R4) "We cannot reach the crash state " ← negation of the simple

- (R5) "We can enter the critical section without traversing n=0 " ← with conditional restricts

- (R6) "We can always return to the initial state " ← stronger / nested

- (R7) "We can return to the initial state "

# 6.1 Reachability in Temporal Logic

• ΕF Φ

- "There exists a path from the current state along which some state satisfying  $\phi$  "

- (R1) "We can obtain n<0 "

- EF (n<0)

- (R2) "We can enter a critical section "

- EF crit\_sec

- (R3) "We cannot have n<0 "

- ¬EF (n<0)

- (R4) "We cannot reach the crash state "

- ¬EF crash

- AG ¬crash

- "Along every path, at any time, ¬crash"

- (R5) "We can enter the critical section without traversing n=0 "

- E (n≠0) U crit\_sec

- " There exists a path along which  $n \neq o$  holds until crit\_sec becomes true. "

- (R6) "We can always return to the initial state "

- AG (EF init)

- (R7) "We can return to the initial state "

- EF init

# 6.2 Model Checkers and Reachability

- Reachability properties are typically the easiest to verify.

- All model checkers can answer it in principle by simply examining their reachability graph.

- But, they do vary in richness.

- conditional reachability

- nested reachability

- etc.

- Design/CPN is specifically designed for reachability property verification.

# 6.3 Computation of the Reachability Graph

- The effective construction of set of reachable states are non-trivial.

- Several automata are synchronized.

- Algorithms dealing with reachability problems

- 1. Forward chaining

- 2. Backward chaining

- 3. "On-the-fly" exploration

- Forward chaining

- A natural approach, from initial states  $\rightarrow$  add their successors  $\rightarrow$  until saturation

- Difficulty:

- Potential explosion of the set constructed

- Backward chaining

- from target states → add immediate predecessors → until saturation, then, test whether some initial states are in there

- Difficulties:

- 1. Target states need to be fixed before.

- 2. Computing immediate predecessors is generally more complicated than that of successors.

- "On-the-fly" exploration

- Explore the reachability graph without actually building it

- Construction is performed partially, as the exploration proceeds, without remembering everything already visited.

- Background assumption

- Present-day computers are more limited in memory resources than in processing speed

- It is efficient mostly when

- 1. Target set is indeed reachable. ("Yes" requires no exhaustive explorations)

- 2. Can operate in forward or backward manners (The forward is the traditional)

- 3. May apply to some systems with infinitely many states

# **Safety Properties**

# 7. Safety Properties

#### Safety property

- Under certain conditions, an (undesirable) event never occur.

#### – Examples:

- (S1) "Both processes will never be in their critical sections simultaneously (mutual exclusion)"

- (S2) " Memory overflow will never occur "

- (S3) " The situation ... is impossible "

- (S4) "As long as the key is not in the ignition position, the car won't start " ← with conditions

- ¬ safety property = reachability property

- ¬ reachability property = safety property

# 7.1 Safety Properties in Temporal Logic

- AG ¬Φ

- " $\phi$  never occurs."

- (S1) "Both processes will never be in their critical sections simultaneously "

- AG ¬(crit\_sec1 ∧ crit\_sec2)

- (S2) "Memory overflow will never occur"

- AG ¬overflow

- (S3) " The situation ... is impossible "

- AG ¬situation

- (S4) "As long as the key is not in the ignition position, the car won't start "

- A (¬start W key) ← using weak until : it is a safety property

- A (¬start U key) ← using strong until : Not a safety property!

# 7.2 A Formal Definition

- Syntactic characterization

- Safety properties can be written in the form AG  $\phi^-$

- $\phi^-$  is a past temporal formula

- When a safety property is violated, it should be possible to instantly notice it.

- We can only notice it, in the current state, relying on events which occurred earlier.

- Temporal logic with past

- CTL\* does not provide past combinators.

- But, we can use a mirror image of future combinators (F<sup>-1</sup>, X<sup>-1</sup>)

- AG  $\phi^-$  in practice

- (S1) AG  $\neg$ (crit\_sec<sub>1</sub>  $\land$  crit\_sec<sub>2</sub>)

- $\neg$ (crit\_sec<sub>1</sub>  $\land$  crit\_sec<sub>2</sub>) is a  $\phi$

- (S4) A ¬start W key

- Can be rewritten in the form: AG (start  $\Rightarrow$  F<sup>-1</sup> key)

- " It is always true (AG) that if the car starts, then ( $\Rightarrow$ ) the key was inserted beforehand (F<sup>-1</sup>). "

# **7.3 Safety Properties in Practice**

- Safety properties are verified simply by submitting it to a model checker. But, in real life, hurdles spring up.

- A simple case: non-reachability

- The most safety properties

- $\neg \mathsf{EF} (\operatorname{crit\_in}_1 \land \operatorname{crit\_in}_2) = \mathsf{AG} \ \boldsymbol{\Phi}^-$

- $\neg(crit\_in_1 \land crit\_in_2)$  is a present formula

- Safety without past

- − A (¬start W key) vs. AG (start  $\Rightarrow$  F<sup>-1</sup> key)

- No model checker is able to deal with past formulas. So, mixed logics are used.

- The problem is their identification.

- $\rightarrow$  If they are identified, then it can be dealt with similarly

- $\rightarrow$  Otherwise, we have to use the method of <u>history variables (in section 7.4)</u>

- Safety with explicit past

- No model checker is able to handle temporal formula with past.

- Two approaches:

- 1. Eliminate the past (in principle, it is possible to translate mixed formulas to pure-future ones)

- AG (φ ⇒ F<sup>-1</sup> ψ) ≡ A (¬φ W ψ), but not easy.

2. History variable method (section 7.4)

## **Liveness Properties**

#### 8. Liveness Properties

- Liveness property

- Under certain conditions, some event will ultimately occur.

- Some happy event will occur in the end.

- Examples:

- (L1) " Any request will ultimately be satisfied "

- (L2) " By keeping on trying, one will eventually succeed "

- (L3) " If we call on the elevator, it will bound to arrive eventually "

- (L4) "The light will turn green (some day regardless of the system behavior)"

- (L5) " After the rain, the sunshine "

- (L6) " The program will terminate "

- Two broad family of liveness properties

- 1. Simple liveness : *progress* (Chapter 8)

- 2. Repeated liveness : *fairness* (Chapter 10)

### 8.1 Simple Liveness in Temporal Logic

- FΦ

- " $\phi$  will ultimately occur. "

- (L1) "Any request will ultimately be satisfied "

- AG (req  $\Rightarrow$  AF sat)

- (L7) "The system can always return to its initial state "

- AG EF init

- PUQ

- "Along the execution, we will find a state satisfying Q and P will hold for all the states encountered in the meantime "

- Regarded as a liveness property

- PUQ ≡ FQ ∧ (PWQ) (liveness) (safety)

- A(PUQ) and E(PUQ) are all liveness properties.

### 8.2 Are Liveness Properties Useful?

- Abstract liveness properties

- "If we call on the elevator, it is bound to arrive eventually "

- It yields no information, from a utilitarian viewpoint.

- "Abstract" liveness property

- "An event will occur within at most x time unit"

- It is useful, but became a safety property.

- "Bounded" liveness property

- But, it is still useful

- "Abstract" is more general than "concrete".

- "Abstract" is more efficient than "concrete".

- "Abstract" and "concrete" are not contradictory.

### 8.3 Liveness in the Model and the Properties

- Two different roles in the verification process

- 1. Liveness properties : we wish to verify

- 2. Liveness hypotheses : we make on the system model

- When we use a mathematical model(automata) to represent a real system,

- The semantics of the model in face define *implicit safety and liveness hypotheses*.

- Safety hypothesis :

- Clear

- It can flip from q to q' only if it includes a transition going from q to q'.

- Liveness hypothesis :

- Not clear

- The system will chain transitions as long as possible to a block state or accepting states.

- "The system does not terminate without reason, or remain inactive indefinitely without reason."

- Can be subtle and cause errors :

In state x, will always end up wishing printing. → Different from the real world's behavior !!!

• One must be aware of the premises of the models used and check their adequacy.

### **8.4 Verification under Liveness Hypotheses**

- Verify that specific model behaviors satisfy a given property :

- $\phi_v$  : only the model which the liveness hypotheses hold

- $\Psi$  : a property

- Verify  $\Phi_v \Rightarrow \psi$  is sufficient.

- If  $\psi$  is a CTL property

- AF ( E PUQ )  $\rightarrow$  A ( $\Phi_v \Rightarrow$  FE ( $\Phi_v \land$  P U Q) )

#### **8.5 Bounded Liveness**

#### Bounded liveness property

- A liveness property that comes with a maximal delay which the desired situation must occur

- Safety properties from a theoretical viewpoint``

- Can be rewritten in a form AG ( $\psi_2 \Rightarrow F^{-1} \psi_1$ )

- Not as important as safety properties

- Bounded liveness in timed systems

- Often used in the specification of timed systems (in Chapter 5)

- Explicit constraints on delays  $\rightarrow$  TCTL !!!

- (BL1) " The program terminates in less than ten seconds "

- $AF_{<10s}$  end  $\leftarrow$  bounded liveness property

- AG ( $\neg$ end  $\Rightarrow$  F<sup>-1</sup><sub><10s</sub> start )  $\leftarrow$  safety property

- (BL2) " Any request is satisfied in less than five minutes "

- AG ( req  $\Rightarrow$  AF<sub><5m</sub> sat )  $\leftarrow$  bounded liveness property

- AG (  $\neg$  (F<sup>-1</sup><sub>=5m</sub>req  $\land$  G<sup>-1</sup><sub>≤5m</sub> $\neg$ sat ) ← safety property

DEPENDABLE SOFTWARE LABORATORY

### **Deadlock-Freeness**

#### 9. Deadlock-Freeness

#### Deadlock-freeness

- A special property, " The system can never be in a situation on which no progress is possible."

- Correct property relevant for systems that are supposed to run indefinitely

- A set of properly identified final states will be required to be deadlock-free.

#### 9.1 Safety? Liveness?

#### AG EX true

- "Whatever the state reached may be (AG), there will exist an immediate successor state (EX true) "

- Not the form of  $AG\phi^1$

- Deadlock-free is not a safety property.

- Can be verified if the model checker can handle AG EX true.

#### 9.2 Deadlock-freeness for a Given Automaton

- We sometimes think of deadlock-freeness as a safety property

- For a given automaton, we can describe the deadlock states explicitly.

- But, it is up to the automaton we obtain.

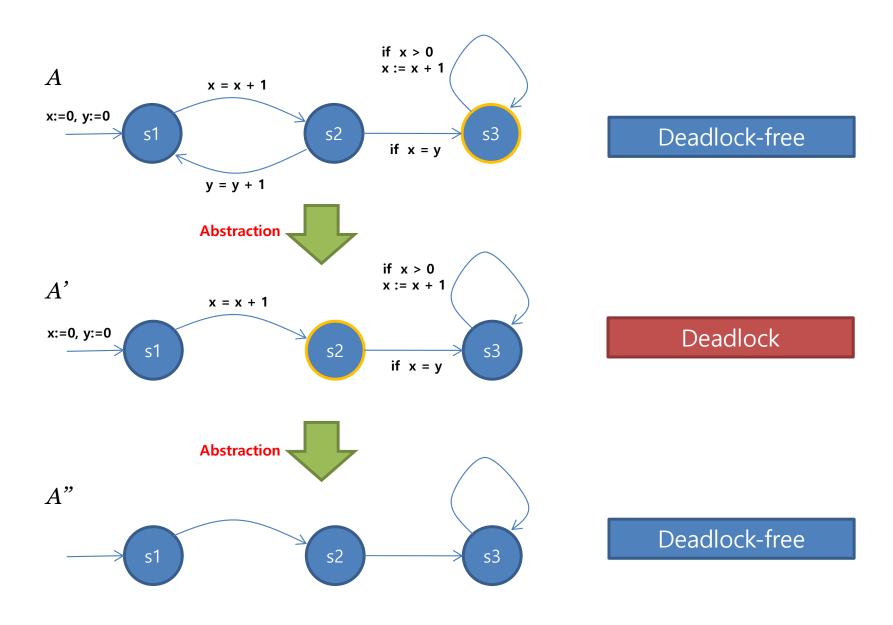

if x > 0x := x + 1 A x = x + 1AG EX true  $\rightarrow$  hold! (liveness property) x:=0, y:=0 AG  $\neg$ (s3  $\land$  x≤0)  $\rightarrow$  hold! (safety property) s2 s3 s1 if x = yy = y + 1 if x > 0x := x + 1 Α' x = x + 1AG EX true  $\rightarrow$  not hold! (liveness property) x:=0, y:=0 AG  $\neg$ (s3  $\land$  x≤0)  $\rightarrow$  hold! (safety property) s2 s3 s1 if x = y

- For example,

#### 9.3 Beware of Abstractions!

DEPENDABLE SOFTWARE LABORATORY

## **Fairness Properties**

#### **10. Fairness Properties**

#### Fairness Property

- Under certain conditions, an event will occur (or will fail to occur) infinitely often

#### - Examples:

- (F1) "The gate will be raised infinitely often"

- (F2) " If access to a critical section is infinitely often requested, then access will be granted infinitely often "

- repeated liveness or repeated reachability

### **10.1 Fairness in Temporal Logic**

- GF P

- "We meet a state in which P holds infinitely often."

- There is no last state in which P holds.

- Fairness properties cannot be expressed in pure CTL

- (F1) " The gate will be raised infinitely often."

→ A ( GF gate\_raised )

- (F2) " If access to a critical section is infinitely often requested, then access will be granted infinitely often."

$\rightarrow$  A ( GF crit\_req  $\Rightarrow$  FG crit\_in )

- FCTL or ECTL+

- CTL + fairness

- O(  $|A| \times |\phi|^2$  )

- <u>Many tools (like SMV) considers the fairness hypotheses as part of model rather than choosing FCTL.</u>

#### **10.2 Fairness and Nondeterminism**

- In practice, fairness properties are used to describe the form of some nondeterministic sequences.

- "When a nondeterministic choice occurs at some point, it is often assumed to be fair."

- For example,

- A die with six faces

- Its behavior is fair, if it fulfills the property:

- A (GF 1 ^ GF 2 ^ GF 3 ^ GF 4 ^ GF 5 ^ GF 6)

- Fairness properties can be viewed as an abstraction of probabilistic properties.

### **10.3 Fairness Properties and Fairness Hypotheses**

- Fairness properties are very often used as hypotheses.

- An example:

- Classical alternating bit protocol

- A : a transmitter

- B : a receiver

- AB : a line for messages

- BA : a line for message acknowledgements

- Messages can be lost  $\rightarrow$  non-deterministic behavior of AB and BA

- Liveness property : "Any emitted message is eventually received."

- G ( emitted  $\Rightarrow$  F received ) : Fail !!!

- The model allows to systematically lose all messages.

- Our original intension : "unreliable" line, not the whole lose  $\rightarrow$  Fairness hypothesis !!!

- A ( GF  $\neg loss \Rightarrow$  G ( emitted  $\Rightarrow$  F received ) ) <u>fairness hypothesis</u> liveness property

- Repeated liveness property : " If infinitely many messages are emitted, then infinitely many messages will be transmitted."

#### repeated liveness property

• A ( GF  $\neg loss \Rightarrow$  ( GF emitted  $\Rightarrow$  GF received ) ) <u>fairness hypothesis</u> ( repeated liveness hypothesis

### **10.4 Strong Fairness and Weak Fairness**

- Fairness property

- "If P is continually requested, then P will be granted (infinitely often)."

- Weak fairness : without interruption

- Strong fairness : possibly with interruption

- No difference when using them for model checking of finite systems

#### Weak fairness

- Assume that P is requested without interruption

- (FG request\_P)  $\Rightarrow$  F P

- (FG request\_P)  $\Rightarrow$  GF P

#### Strong fairness

- Assume that P is requested in an infinitely repeated manner, possibly with interruptions

- (GF request\_P)  $\Rightarrow$  F P

- (GF request\_P)  $\Rightarrow$  GF P

### 10.5 Fairness in the Model or in the Property?

- The best way is

- Model = automaton + fairness hypothesis

- Pros: Fairness hypothesis can change independently from the automata model.

- Ex. SMV model checker

- Symbolic Model Checking

- Timed Automata

# **FORMAL VERIFICATION : ADVANCED**

# **5. Symbolic Model Checking**

### 4. Symbolic Model Checking

#### • Symbolic model checking

- Any model checking method attempting to <u>represent symbolically</u> states and transitions

- A particular symbolic method in which BDDs(Binary Decision Diagram) are used to represent the state variables

- Represent very large sets of states concisely, as if they were in bulk.

- Motivation:

- State explosion is the main problem for CTL or PLTL model checking.

- State explosion occurs whenever we represent explicitly all states of automaton we use.

- Organization

- Symbolic Computation of State Sets

- Binary Decision Diagrams (BDD)

- Representing Automata by BDDs

- BDD-based Model Checking

### 4.1 Symbolic Computation of State Sets

- Iterative computation of  $Sat(\phi)$

- A = <Q, T, ... >

- Pre(S) : immediate predecessors of the states belonging to S in Q

- **Sat**( $\phi$ ) : set of states of A which satisfy  $\phi$

- $\psi$  is the sub-formulas of  $\phi$

- Sat( $\neg \psi$ ) = Q \ Sat( $\psi$ )

- − Sat( $\psi \land \psi$ ) = Sat( $\psi$ ) ∩ Sat( $\psi$ )

- Sat(EX  $\psi$ ) = Pre(Sat( $\psi$ ))

- Sat(AX  $\psi$ ) = Q \ Pre(Q \ Sat( $\psi$ ))

- Sat(EF  $\psi$ ) = Pre\*(Sat( $\psi$ ))

- ... (others are defined in a similar way)

```

/* ==== Computation of Pre*(S) ==== */

X := S;

Y := { };

while (Y != X) {

Y := X;

X := X \vee Pre(X);

}

return X;

```

- The algorithms in Section 3.1 is an particular implementation of  $Sat(\phi)$

- Hence,  $Sat(\phi)$  is an explicit representation of the state sets.

- Which symbolic representations to use ?

- We have to access the following primitives:

- 1. A symbolic representation of Sat(P) for each proposition  $P \subseteq Prop$ .

- 2. An algorithm to compute a symbolic representation of Pre(S) from a symbolic representation of *S*.

- 3. Algorithms to compute the complement, the union, and the intersection of the symbolic representations of the sets.

- 4. An algorithm to tell whether two symbolic representations represent the same set.

- Systems with infinitely many states

- Symbolic approach naturally extends to infinite systems.

- New difficulties:

- 1. Much trickier to come up with symbolic representations.

- 2. Iterative computation  $Sat(\phi)$  is no longer guaranteed to terminate.

### 4.2 Binary Decision Diagram (BDD)

#### • BDD

- A particular data structure very commonly used for representing states sets symbolically

- Proposed in 1980s ~ early in 1990s

- Make possible the verification of the system which cannot represent explicitly.

- Advantages:

- Efficiency

- Simplicity

- Easy Adaptation

- Generality

- BDD structure example

- *n* boolean variables  $x_1, x_2, \dots, x_n$  associated with a tuple  $\langle b_1, b_2, \dots, b_n \rangle$

- Suppose n = 4,

- The set S of our interest is the set such that  $(b_1 \vee b_3) \wedge (b_2 \Rightarrow b_4)$  is true.

- We have several ways to represent the set:

- S = {<F,F,T,F>, <F,F,T,T> , ... >

- S =  $(b_1 \vee b_2) \wedge (b_3 \Rightarrow b_4)$

- $S = (b_1 \land \neg b_2) \lor (b_1 \land b_4) \lor (b_3 \land \neg b_2) \lor (b_3 \land b_4) \leftarrow DNF$

- .

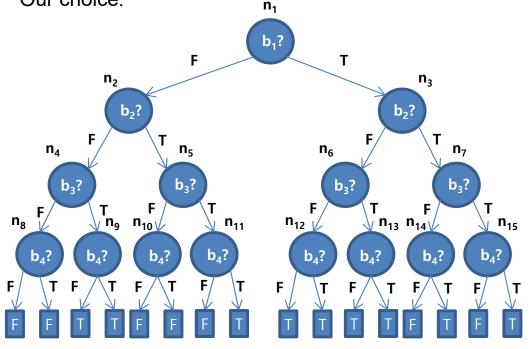

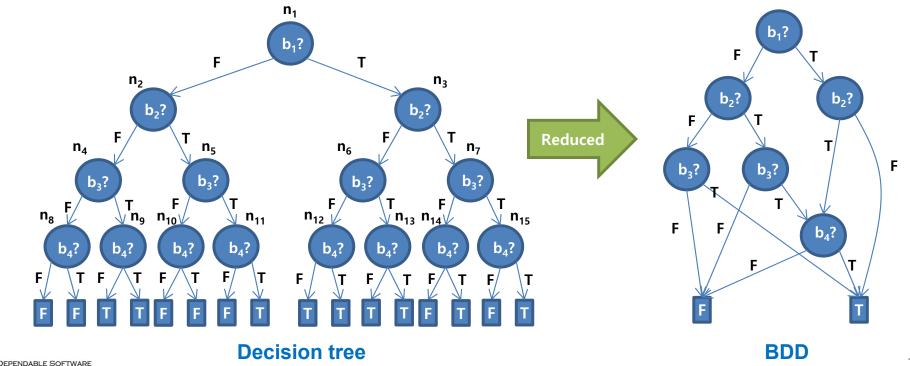

- **<u>Decision Tree</u>** ← Our choice.

- Decision tree reduction

- A <u>BDD</u> is a reduced decision tree.

- Reduction rules:

- 1. Identical sub-trees are identified and shared. ( $n_8$  and  $n_{10}$ )

- $\rightarrow$  leads to a directed acyclic graph (dag)

- 2. Superfluous internal nodes are deleted.  $(n_7)$

- Advantages:

LABORATORY

- 1. Space saving

- 2. Canonicity

- Canonicity of BDDs

- BDDs canonically represent sets of boolean tuples. (fundamental property of BDDs)

- If the order of the variable  $x_i$  is fixed, then there exists a unique BDD for each set *S*.

- Properties of BDDs

- 1. We can test the equivalence of two BDDs in constant time.

- 2. We can tell whether a BDD represents the empty set simply by verifying whether it is reduced to a unique leaf F.

- Operations on BDDs

- All boolean operations

- 1. Emptiness test

- 2. Comparison

- 3. Complementation

- 4. Intersection

- 5. Union and other binary boolean operations

- 6. Projection and abstractions

- Complexity : linear or quadratic (for each operation)

- $\rightarrow$  The same state explosion problems still exist.

#### 4.3 Representing Automata by BDDs

- Before applying BDDs to symbolic model checking, we need to restate

- Representing the <u>states</u> by BDDs

- Representing <u>transitions</u> by BDDs

- Representing the states by BDDs

- Consider an automaton A with

- $Q = \{q_0, \dots, q_6\} \rightarrow b_1^1, b_1^2, b_1^3$

- var digit:0..9  $\rightarrow b_{2}^{1}, b_{2}^{2}, b_{2}^{3}, b_{2}^{4}$

- var ready:bool  $\rightarrow b_3^1$

- $< b_1^1, b_1^2, b_1^3, b_2^1, b_2^2, b_2^3, b_2^4, b_3^1 >$

- < F, T, T, T, F, F, F, F > = < $q_3$ , 8, F >

- Let's represent  $Sat(ready \Rightarrow (digit > 2))$

- States  $\langle q, k, b \rangle$  such that if b = T and k > 2

- ready  $\Rightarrow$  (digit > 2)  $\equiv \neg$  ready  $\lor$  (digit > 2)

- Representing transitions by BDDs

- The same idea is applied.

- $\langle q_3, 8, F \rangle \rightarrow \langle q_5, 0, F \rangle : \langle F, T, T, T, F, F, F, F, F, T, F, F, F, F, F, F, F \rangle$

- For example,

$$\begin{array}{l} \boldsymbol{\rightarrow} ( \neg b_{1}^{1} \wedge \neg b_{1}^{2} \wedge b_{3}^{1} ) \\ \wedge ( b_{2}^{1} \vee b_{2}^{2} \vee b_{3}^{2} \vee b_{4}^{2} ) \\ \wedge ( \neg b_{1}^{1} \wedge b_{2}^{1} \wedge \neg b_{3}^{1} ) \\ \wedge ( b_{2}^{1} \Leftrightarrow b_{2}^{1} \wedge b_{2}^{2} \Leftrightarrow b_{2}^{2} \wedge b_{3}^{2} \Leftrightarrow b_{3}^{3} \wedge b_{4}^{2} \Leftrightarrow b_{4}^{4} ) \\ \wedge b_{1}^{1} & \end{array}$$

### 4.4 BDD-based Model Checking

- BDDs can serve as an instance of symbolic model checking scheme.

- Provide compact representations for the sets of states in an automaton

- Support the basic sets of operations

- Computation of Pre(S) in section 4.1 is very simple.

- Implementation

- SMV (chapter 12)

- Efficiency of BDDs depends on

- $B_T$  representing the transition relation T (as containing pairs of states)

- Choice of ordering for the boolean variables

- Very easy to explode exponentially.

- Perspective

- Widely used from early 1990s

- Current work on model checking

- Aiming at applying BDD technology to solve more verification problems (ex. program equivalence)

- Aiming at extending the limits inherent to BDD-based model checking

- Widely used throughout the VLSI design industry.

# 6. Timed Automata

# 5. Timed Automata

### • "Temporal"

"Trigger the alarm action upon detecting a problem"

### • "Real-Time"

"Trigger the alarm less than 5 seconds after detecting a problem"

### <u>Timed Automata</u>

- Proposed by Alur and Dill in 1994.

- An answer to this "real-time" needs

### Organization

- Description of a Timed Automata

- Networks of Timed Automata and Synchronization

- Variants and Extensions of the Basic Model

- Timed Temporal Logic

- Timed Model Checking

# **5.1 Description of Timed Automata**

- Two fundamental elements of timed automata

- 1. A finite automaton (assumed instantaneous between states)

- 2. Clocks

• An example

- Clocks and transitions

- Clocks

- Variables having non-negative real values in *R*

- All clocks are null in the initial system states.

- All clocks evolve at the same speed, synchronously with time.

### – Transitions

- Three items

- A guard

- An action (label)

- Reset of some clocks

- The system operates as if equipped with

- <u>A global clock</u>

- Many individual clocks (each is synchronized with the global clock)

- Configurations and executions

- Configuration of the system

- (q, v)

- q : a current control state of the automaton

- v: the value of each clock

- We also refer to *v* as a valuation of the automaton clocks.

- Timed automata does not fix the time unit under consideration

- **Execution** of the system

- (usually infinite) sequence of configurations

- A mapping  $\rho$  from *R* to the set of configuration

- Configurations change in two ways

- Delay transition

- Discrete transition (or action transition)

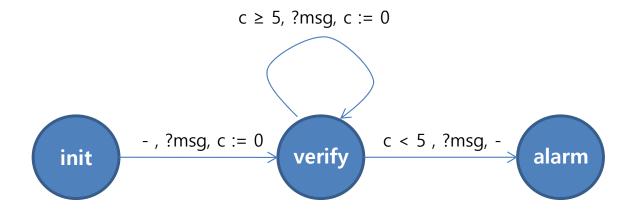

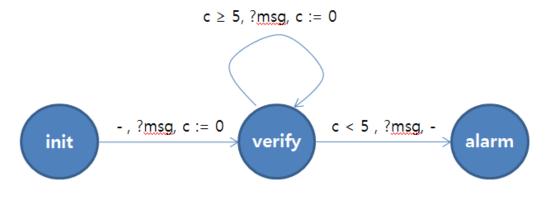

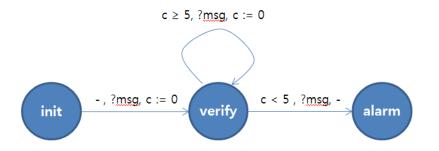

#### **Discrete transition**

$(\text{init, } 0) \rightarrow (\text{init, } 10.2)^{\stackrel{?msg}{\rightarrow}} (\text{verify, } 0) \rightarrow (\text{verify, } 5.8)^{\stackrel{?msg}{\rightarrow}} (\text{verify, } 0) \rightarrow (\text{verify, } 3.1)^{\stackrel{?msg}{\rightarrow}} (\text{alarm, } 3.1) \rightarrow \dots$

- Trajectory

- $-\rho(0)$ : the initial state

- $-\rho(12.3) = (verify, 2.1)$

# **5.2 Networks of Timed Automata and Synchronization**

- It is useful to build a timed model in a composite fashion, by combining several parallel automata synchronized with one another.

→ a timed automata network

- Executions of a timed automata network

- All automata components run in parallel at the same speed

- Their clocks are all synchronized to the same global clock

- (q, v): a network configuration

- *q* : a control state vector

- v: a function associating each network clock with its value at the current time

### Synchronization

- Timed automata synchronize on transitions (as usually) by resetting the clocks.

- The clocks which were not reset are unchanged.

- No concurrent write conflicts on clocks, since reset writes a zero value and nothing else.

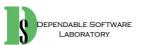

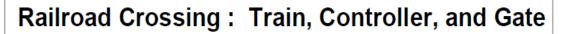

### • Example : modeling a railroad crossing

# **5.3 Variants and Extensions of the Basic Models**

- Many variants, and three extensions

- Invariants

- Liveness hypothesis in the untimed model

- Invariant: a state's condition on the clock values, which must always hold in the state

- Example: near (invariant: Ht < 5), on (invariant: Ht < 2), lower/raise (invariant: Hb < 2)</li>

- Urgency

- Used when cannot tolerate a time delay

- Represented in the system configurations, not in the transitions

- Allowing urgent/synchronized behaviors in a more natural way

- Hybrid linear system

- Models dynamic variables (in a form of differential equations)

- HyTech

# **5.4 Timed Temporal Logic**

- Given a system described as a network of timed automata, we wish to be able to state/verify properties of this system

- Temporal properties

- "When the train is inside the crossing, the gate is always closed."

- Real-time properties

- "The train always triggers an Exit signal within 7 minutes of having emitted an App signal."

- Three ways to formally state real-time properties

- 1. Express it in terms of the reachability of some sets of configurations

- 2. Use observer automata in PLTL model checking

- Given a property  $\phi$ , a network R

- Testing reachability of some states in the product R || A $\phi$

- UPPAAL , HYTECH

- 3. Use a timed logic

- TCTL (Timed CTL), etc.

### • TCTL (Timed CTL)

- $\begin{array}{ll} \bullet & \Phi \ , \ \psi \colon := P_1 \mid P_2 \mid ... & (atomic proposition) \\ & \mid \neg \phi \mid \phi \land \psi \mid \phi \Rightarrow \psi \mid ... & (boolean combinators) \\ & \mid \mathsf{EF}_{(\sim k)} \phi \mid \mathsf{EG}_{(\sim k)} \phi \mid \mathsf{E} \phi \cup_{(\sim k)} \psi & (temporal combinators) \\ & \mid \mathsf{AF}_{(\sim k)} \phi \mid \mathsf{AG}_{(\sim k)} \phi \mid \mathsf{A} \phi \cup_{(\sim k)} \psi & (path quantifiers) \end{array}$

- ~ : any comparison symbol from  $\{<, \leq, =, \geq, >\}$

- k : any rational number from Q. (real number)

- Operator X does not exist in TCTL

- Example :

- AG (pb  $\Rightarrow$  AG<sub>( $\leq 5$ )</sub> alarm)

- "If a problem occurs, then the alarm will sound immediately and it will sound for at least 5 time units."

- AG  $(\neg far \Rightarrow AF_{(<7)} far)$

- "When the train is located in the railway section between the two sensors App and Exit, it will leave this section before 7 time units."

## **5.5 Timed Model Checking**

- With timed automata and TCTL logic

- We wish to obtain a model checking algorithm for them.

- Difficulties : Automaton has an infinite number of configurations, since

- Clock values are unbounded

- The set of real numbers used in clocks is dense

- Overcome it with the equivalence classes, called "regions"

- Example: x1, x2 ~ k with k = 0, 1, 2

- 28 regions

### • Complexity

- Model checking algorithms are complicated.

- The number of regions grows exponentially.

- O(n!M<sup>n</sup>)

- n: number of clocks

- M: upper bounds of every constant

- No general and efficient method is likely to exist. (vs. linear complexity in CTL)

- PSPACE-complete problem

- Existing tools focus on defining adequate data structures for handing sets of regions

*→* "*zones*"

- Existing tools have been successfully used

- UPPAAL

- HyTech

- (KRONOS)

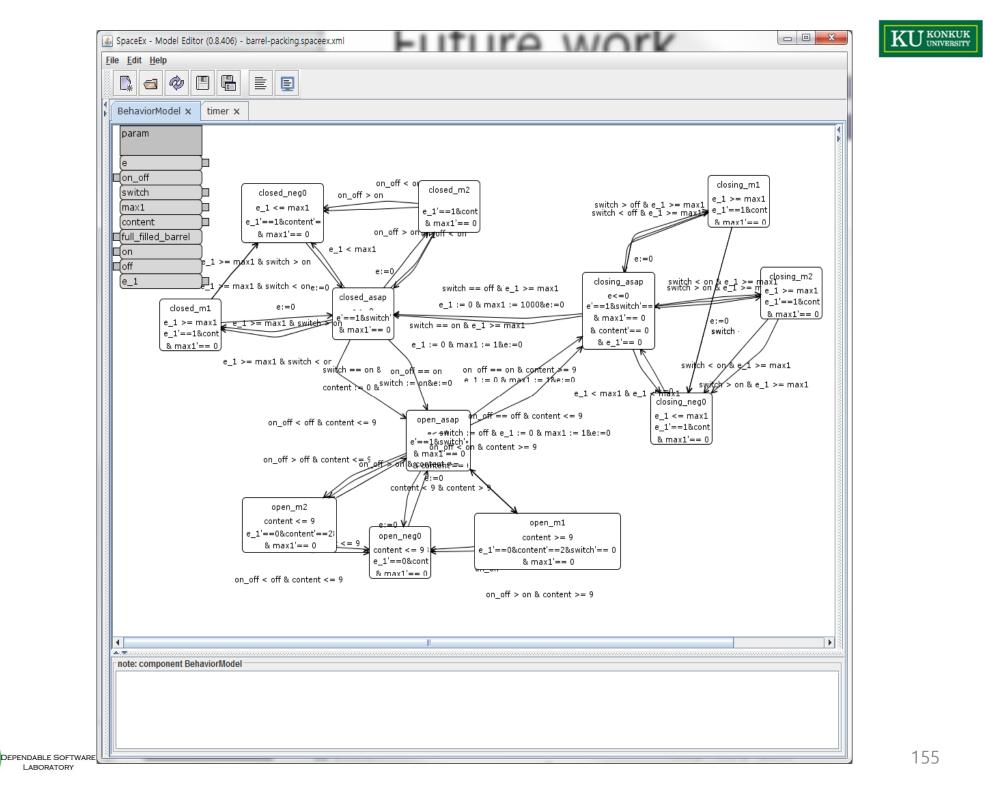

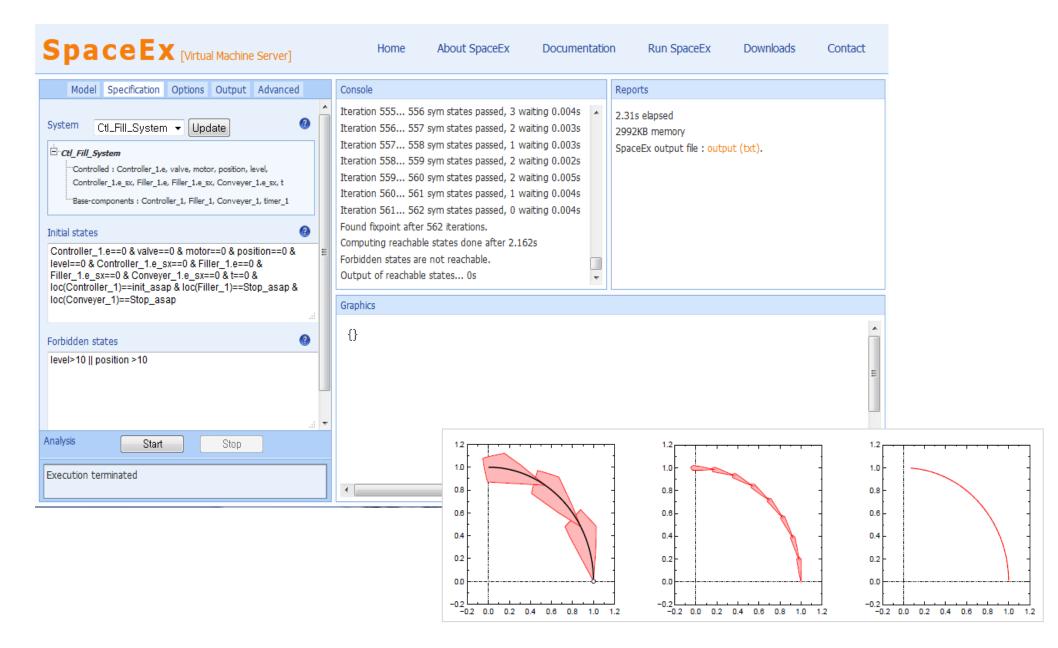

- SpaceEx (PHAver) ← for Hybrid System (CPS)

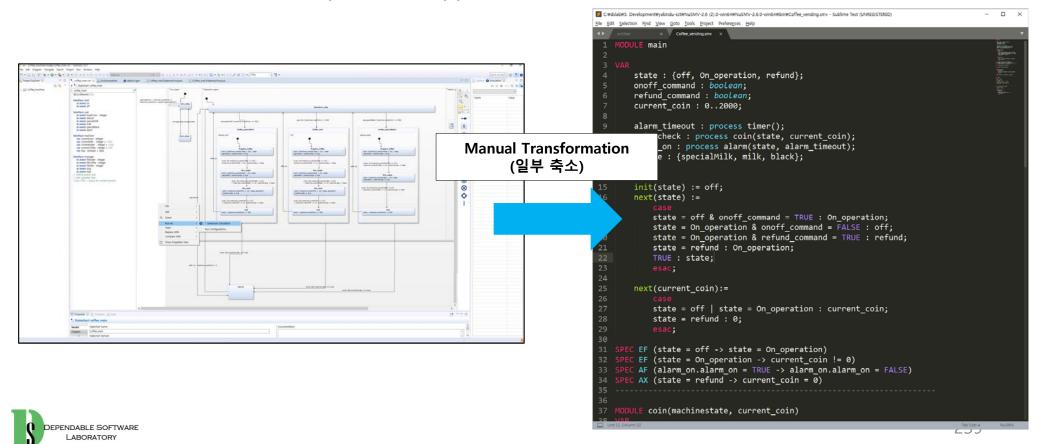

# FORMAL VERIFICATION TOOLS AND CASE STUDIES

# 7. Formal Verification Tools

## Introduction

- Formal modeling methods and tools (graphical methods only)

- SCR

- NuSCR (NuSRS)

- Statecharts Statemate MAGNUM)

- RSML / SpecTRM

- Petri-Nets (Design/CPN)

- Timed Automata (UPPAAL)

- Formal verification (model checking) tools

- SMV

- SPIN

- VIS

- CBMC

- DESIGN/CPN

- UPPAAL

- HyTech

# SCR

### Software Cost Reduction (SCR) <sup>1)</sup>

<sup>1)</sup> http://www.nrl.navy.mil/itd/chacs/5546/SCR

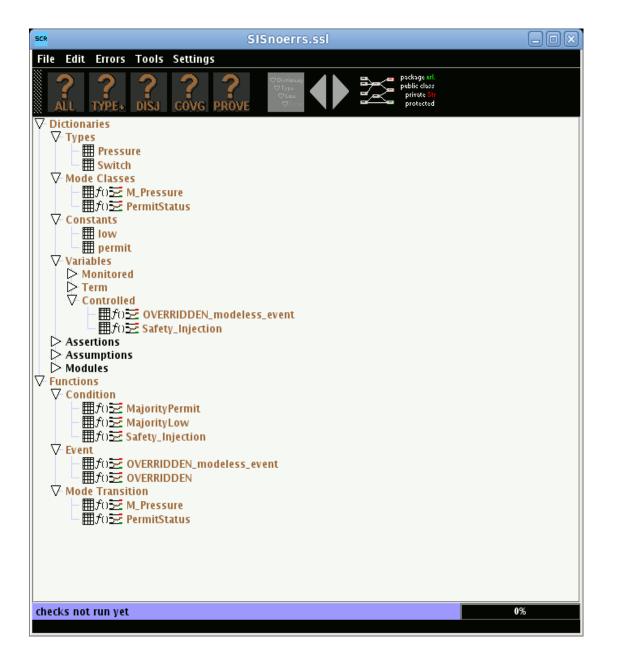

#### **Main Window**

- Condition table

- Event table

- Mode Transition table

#### Editor

The specification consists of two basic types of tables. The first is dictionaries, which describe the types used in the specification, variables, and other objects used to describe the specification with the second table type.

The second type of table describes functions; that is, given certain events or conditions, and the current state of the application, what is the output value of a given variable?

The tables include editing functions for building and changing the developing specification.

| TYPE+                         |     |       |   |            |               |          |       |         | ☑ Mon<br>☑ Term<br>☑ Con | 🗹 Match Case | Name<br>Contains |

|-------------------------------|-----|-------|---|------------|---------------|----------|-------|---------|--------------------------|--------------|------------------|

| Name                          | DGB | Class |   | Туре       | Initial Value | Accuracy | Table | Kind    | Value                    |              | Comment          |

| Block                         | DGB | Mon   | • | Switch 👻   | OFF 🔻         | N/A      | -     | -       |                          |              |                  |

| MajorityLow                   | DGB | Term  | • | Boolean 👻  | TRUE 🔻        | 0        | Т     | Table 🔻 |                          |              |                  |

| MajorityPermit                | DGB | Term  | • | Boolean 👻  | TRUE 🔻        | 0        | Т     | Table 🔻 |                          |              |                  |

| OVERRIDDEN                    | DGB | Term  | • | Boolean 💌  | TRUE 🔻        | 0        | Т     | Table 🔻 |                          |              |                  |

| OVERRIDDEN_model<br>ess_event | DGB | Con   | • | Boolean 🔻  | TRUE -        | 0        | т     | Table 🔻 |                          |              |                  |

| PB                            | DGB | Mon   | • | Pressure 💌 | 14            | 0.05%    | -     | -       |                          |              |                  |

| PG                            | DGB | Mon   | • | Pressure 🔻 | 14            | 0.05%    | -     | -       |                          |              |                  |

| PR                            | DGB | Mon   | • | Pressure 🔻 | 14            | 0.05%    | -     | -       |                          |              |                  |

| Reset                         | DGB | Mon   | • | Switch 🔻   | OFF 🔻         | N/A      | -     | -       |                          |              |                  |

| Safety_Injection              | DGB | Con   | - | Switch 🔻   | OFF 👻         | N/A      | Т     | Table 🔫 | 1                        |              |                  |

| Notes                         |     |       |   |            |               |          |       |         |                          |              |                  |

#### **Consistency Checker**

This checks for correctness and consistency in the tables that describe the specification. Kinds of checks done are syntax and type checking, circular definitions, missing cases, undefined variables, and non-determinism. Any errors found are displayed in the main window under the affected object, making it easy for the user to locate and correct the error.

| SCR                         | Safety_Injection Cond                  | ition Function        | - O X    |

|-----------------------------|----------------------------------------|-----------------------|----------|

| File                        |                                        |                       |          |

| TYPE+ DISJ COVG             |                                        | ×.                    |          |

| E C                         | Safety_Injection Co<br>Defines a Contr | olled Variable        |          |

| Name Safety_Injection       |                                        | Mode Class M_Pressure |          |

| Modes                       | Conditions                             |                       | Comments |

| Normal                      | FALSE                                  | TRUE                  |          |

| Low                         | NOT OVERRIDDEN                         | OVERRIDDEN            |          |

| VoterFailure                | TRUE                                   | FALSE                 |          |

| Safety_Injection =          | ON                                     | OFF                   |          |

|                             |                                        |                       |          |

|                             |                                        |                       |          |

|                             |                                        |                       |          |

| ☐ ☐ ∰f() 🔀 Safety_Injection |                                        |                       |          |

|                             |                                        |                       |          |

|                             |                                        |                       |          |

|                             |                                        |                       |          |

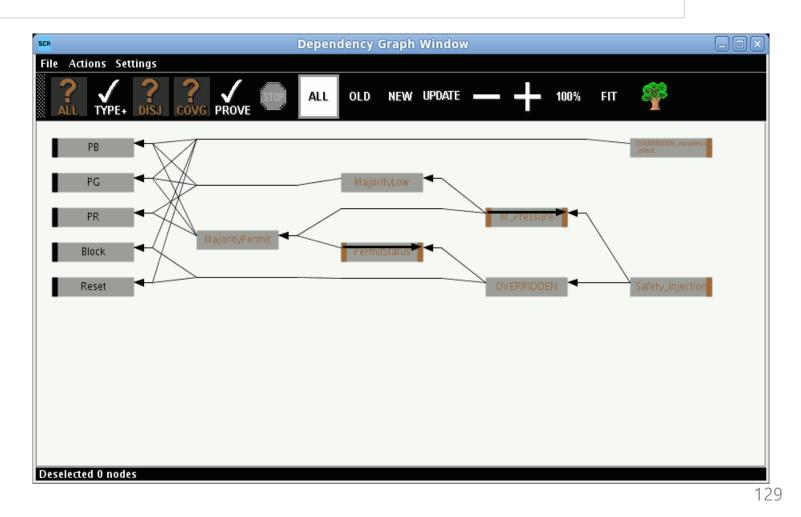

#### **Dependency Browser**

DEPENDABLE SOFTWARE LABORATORY

An existing specification is analyzed to find which objects in the specification depend on which other objects (eg, variables), and a graph of the dependency relationship is created and displayed by this component.

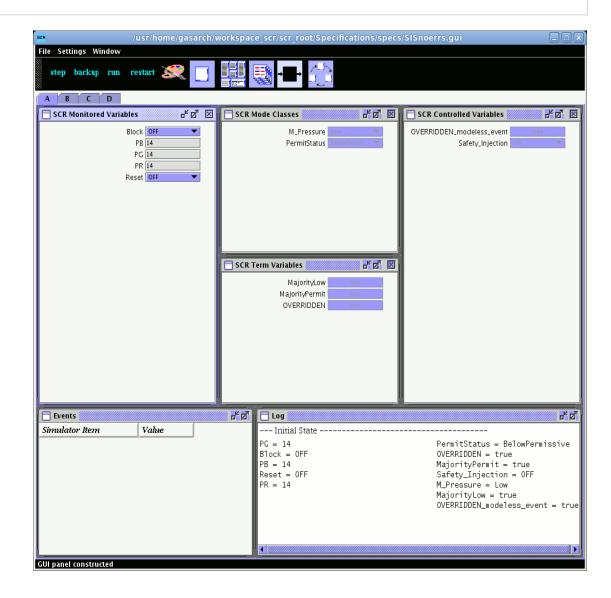

This allows the user to create scenarios, and play them out to check that the specification behaves as expected. The simulator can be run from within the SCR toolset, or it can run separately when code is generated from the specification (one of the functions of the toolset). Simulator

#### Simulator

The simulator display takes two basic forms. One is an automatically generated tabular display, [associate with the simulator.gif] and the other is graphical, tailored to specific applications. This version requires user extensions, based on a framework built into the toolset.

# NuSCR

### NuSCR

A Formal requirements specification language customized for nuclear I&C systems

- Customizing SCR for nuclear domain

- Consisting of 4 constructs

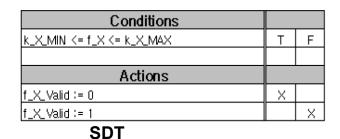

- + SDT (Structured Decision Table)

- + FSM (Finite State Machine)

- + TTS (Timed Transition System)

- + FOD (Function Overview Diagram)

- Various Supporting for seamless verification and safety analysis

- A starting point of the NuDE framework

**Regular Paper** Journal of Computing Science and Engineering, Vol. 11, No. 1, March 2017, pp. 9-23

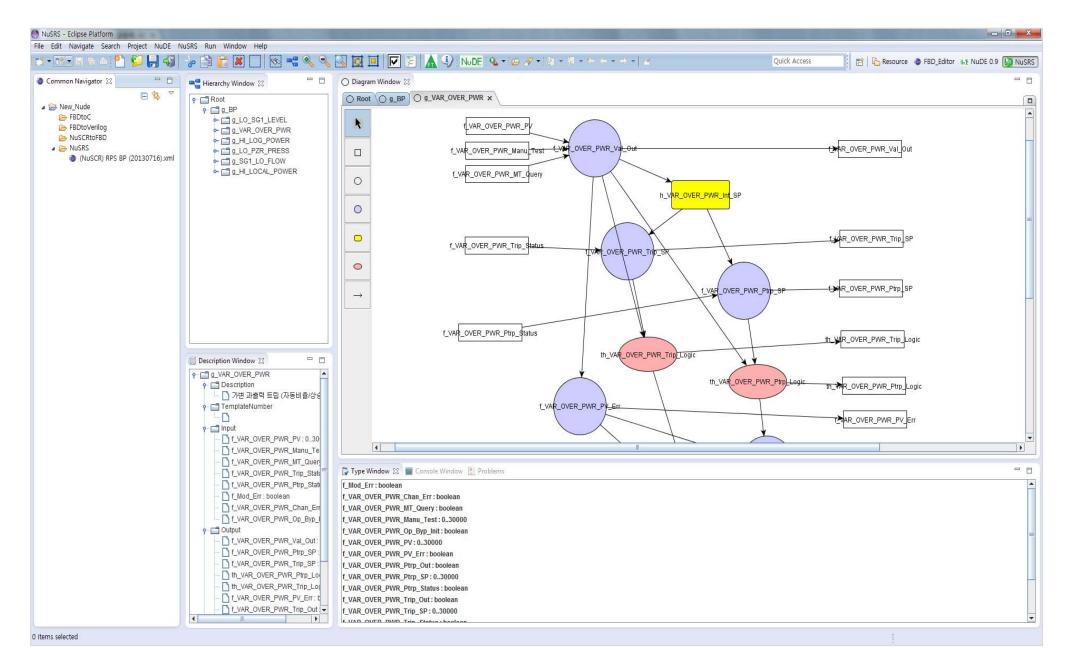

#### NuDE 2.0: A Formal Method-based Software Development, Verification and Safety Analysis Environment for Digital I&Cs in NPPs

Eui-Sub Kim, Dong-Ah Lee, Sejin Jung, and Junbeom Yoo<sup>\*</sup> Division of Computer Science and Engineering, Konkuk University, Seoul, Korea atang34@konkuk.ac.kr, Idalove@konkuk.ac.kr, jsjj0728@konkuk.ac.kr, jbyoo@konkuk.ac.kr

#### DEPENDABLE SOFTWARE LABORATORY

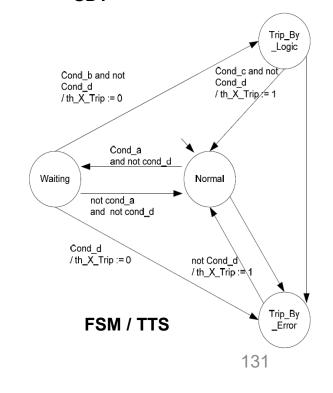

#### NuSRS – NuSCR Modeling Environment

132

DEPENDABLE SOFTWARE LABORATORY KU KONKUK UNIVERSITY

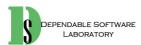

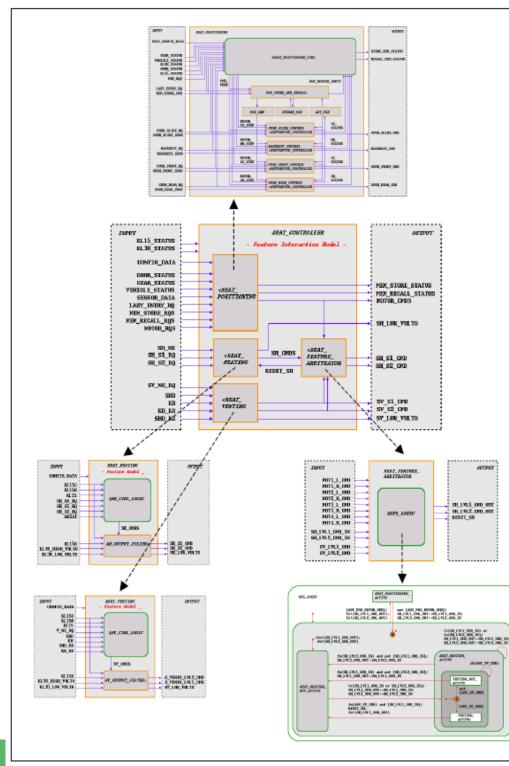

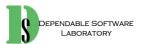

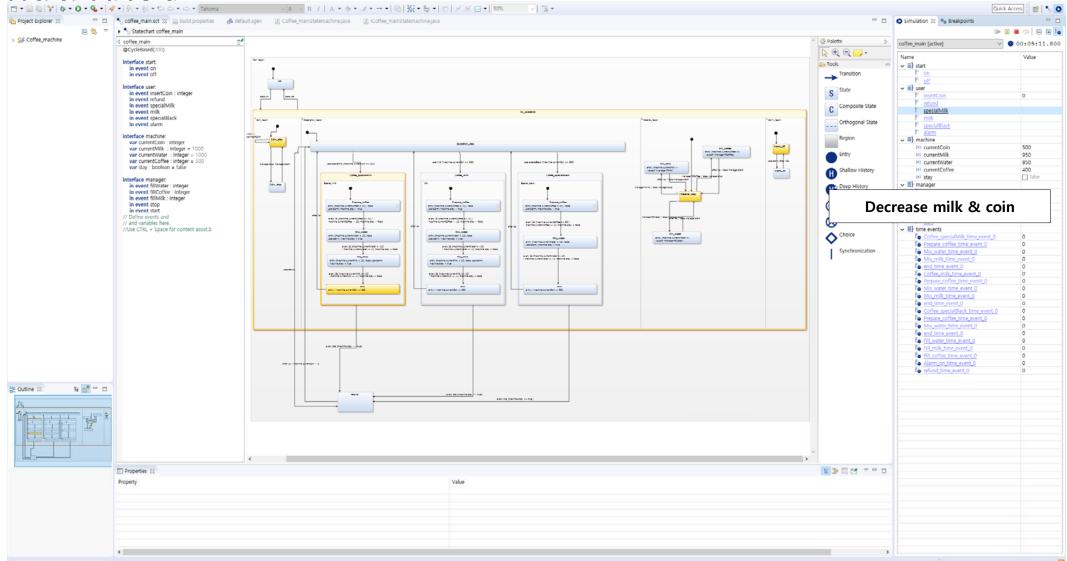

## **Statecharts**

### IBM Rational Statemate MAGNUM

A graphical working environment developed by David Harel

- Create a visual, graphical specification that clearly and precisely represents the intended functions and behavior of the system

- The Statecharts specification may be executed, or graphically simulated

- The 3 views of the system mode

- + Module-charts

- + Activity-charts

- + Statecharts

- Generates C, Ada, VHDL and Verilog code

- Formal verification through in-house model checker

Ativity-chart

KU KONKUK UNIVERSITY

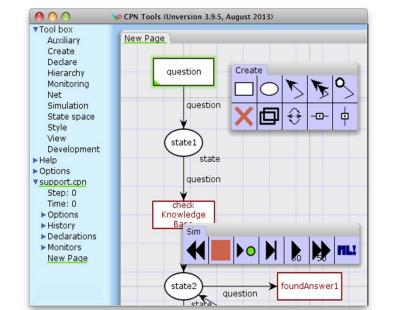

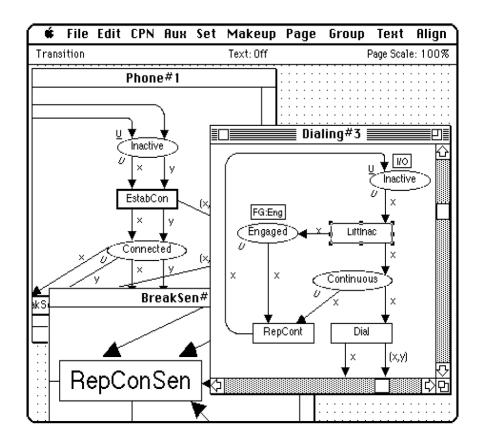

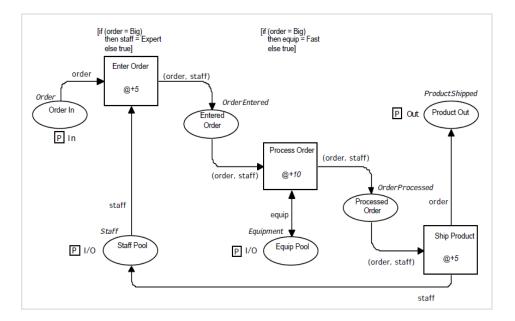

## **Design/CPN**

### Design/CPN (CPN Tools 4.0)

1) http://cpntools.org/

A tool for editing, simulating, and analyzing Colored Petri nets<sup>1)</sup>

- CPN Editor : construction, modification and syntax check of CPN models (CPN Editor)

- CPN Simulator : interactive and automatic simulation of CPN models (CPN Simulator) + simulation-based performance analysis of CPN models

- Occurrence Graph Tool : construction and analysis of occurrence graphs for CPN models → state spaces or reachability graphs/trees

PENDABLE SOFTWARE

LABORATORY

| y MSC                  | Binder 7                                                                                                                                                            |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | ew Page                                                                                                                                                             |

| Sender Receiver        | val msc = MSC.createMSC ("My MSC")                                                                                                                                  |

| product                | MSC.addProcess(msc, "Sender");<br>MSC.addProcess(msc, "Receiver")                                                                                                   |

| e consume              | MSC.addInternalEvent(msc, "Sender", "produce");<br>MSC.addEvent(msc, "Sender", "Receiver", "product");<br>MSC.addEvent(msc, "Receiver", "Receiver", "consume")      |

| Packet 1               |                                                                                                                                                                     |

| product 1              | MSC addl ine(msc "Packet 1")<br>val e1 = "evento" : string<br>val e2 = "event1" : string<br>val e3 = "event2" : string                                              |

| product 2<br>product 3 | val e1 = MSC.startEvent(msc, "Sender", "product 1");<br>val e2 = MSC.startEvent(msc, "Sender", "product 2");<br>val e3 = MSC.startEvent(msc, "Sender", "product 3") |

|                        |                                                                                                                                                                     |

## **Timed Automata**

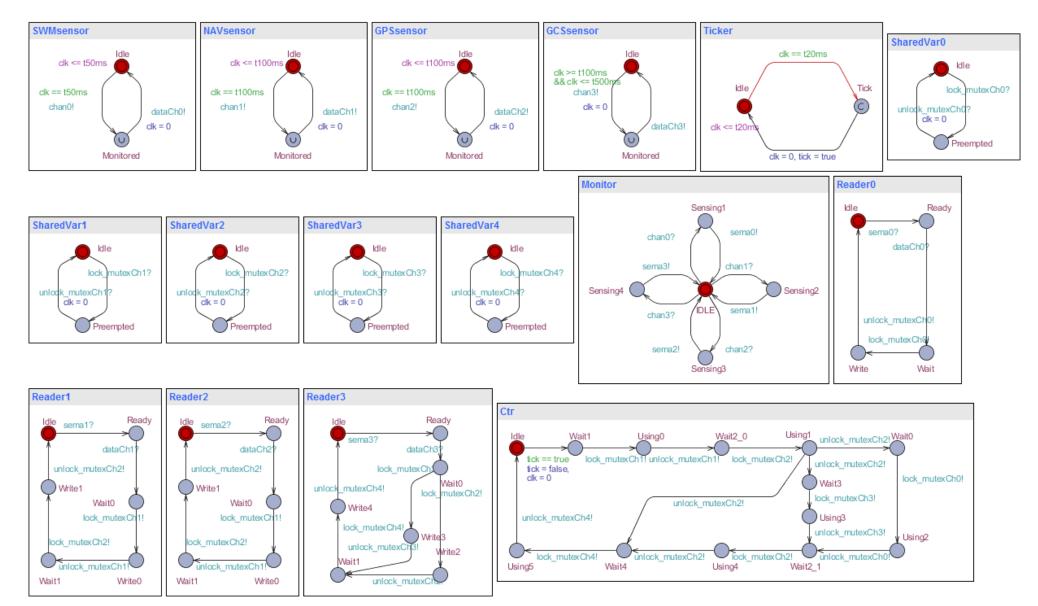

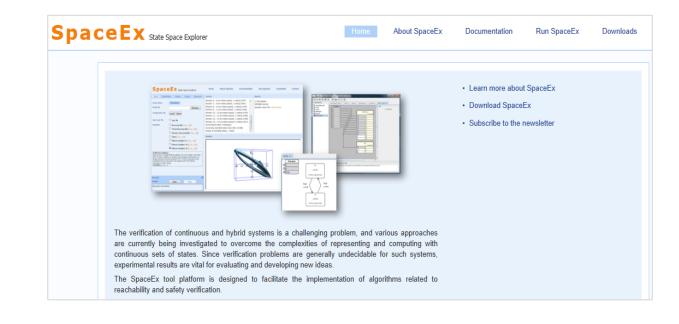

Timed Automata (UPPAAL)

1) http://www.uppaal.org/

An integrated tool environment for modeling, validation and verification of real-time systems modeled as networks of timed automata, extended with data types (bounded integers, arrays, etc.) <sup>1)</sup>

- Use timed automata to analyze timed systems

- Graphical editor

- Graphical simulator

- Verifier

- Model checking

- + CTL reachability analysis based on AG / EF

#### Timed automata models in UPPAAL

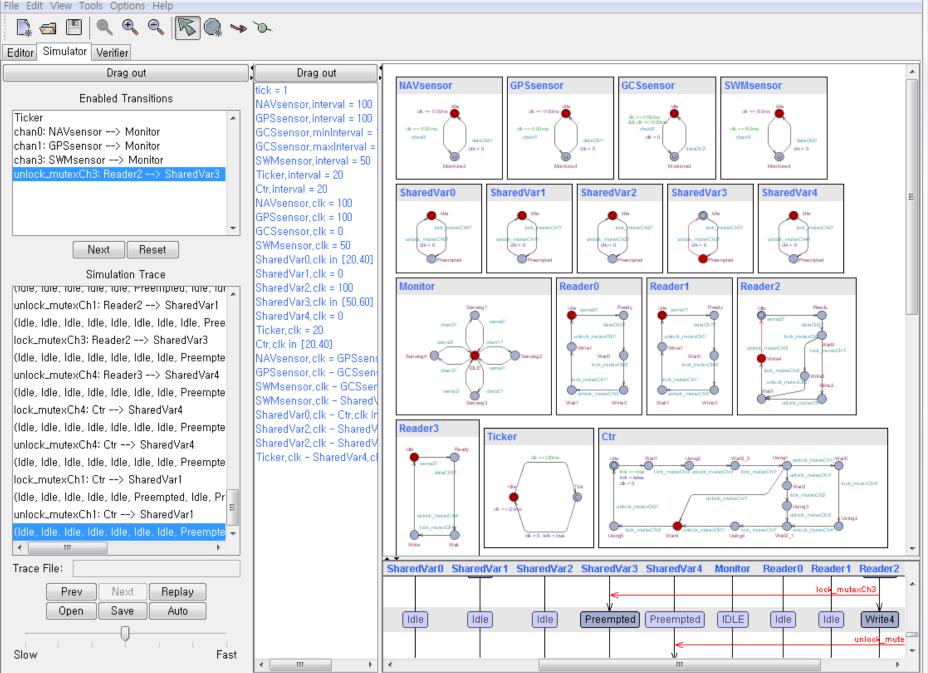

| D:/ITRC/건국대 ITRC/uppaal/new/013.xml - UPPAAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| e Edit View Tools Options Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |

| 💽 🚭 🖳 🔍 🔍 🚫 🚱 🤝 🍉<br>ditor Simulator Verifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| A[] !(Ctr.Wait4 && Ctr.clk > t20ms && Reader2.Write4)         A[] !(Ctr.Wait3 && Ctr.clk > t20ms && Reader2.Write3)         A[] !((Ctr.Wait2_0    Ctr.Wait2_1) && Ctr.clk > t20ms && (Reader0.Write1            A[] !((Ctr.Wait1 && Ctr.clk > t20ms && (Reader0.Write1                                                                                                                                                                                                                                                                                                                                             | Check<br>Insert<br>Remove |

| A[] !(Ctr.WaitO && Ctr.clk > t2Oms && Reader3.Write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Comments                  |

| Query                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           |

| Comment<br>Controller doesn't wait to access SharedVar4 over 20 ms while Reader2 accesses SharedVar4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |

| ▼<br>Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

| A[] !(Ctr, Wait4 && Ctr, clk > t20ms && Reader2, Write4)<br>Property is not satisfied,<br>A[] !(Ctr, Wait3 && Ctr, clk > t20ms && Reader2, Write3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | *                         |

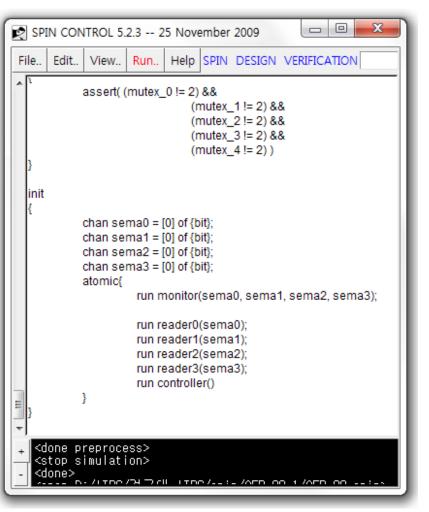

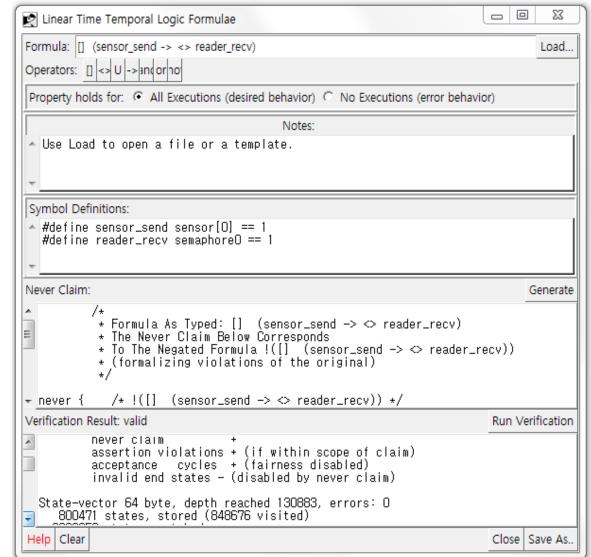

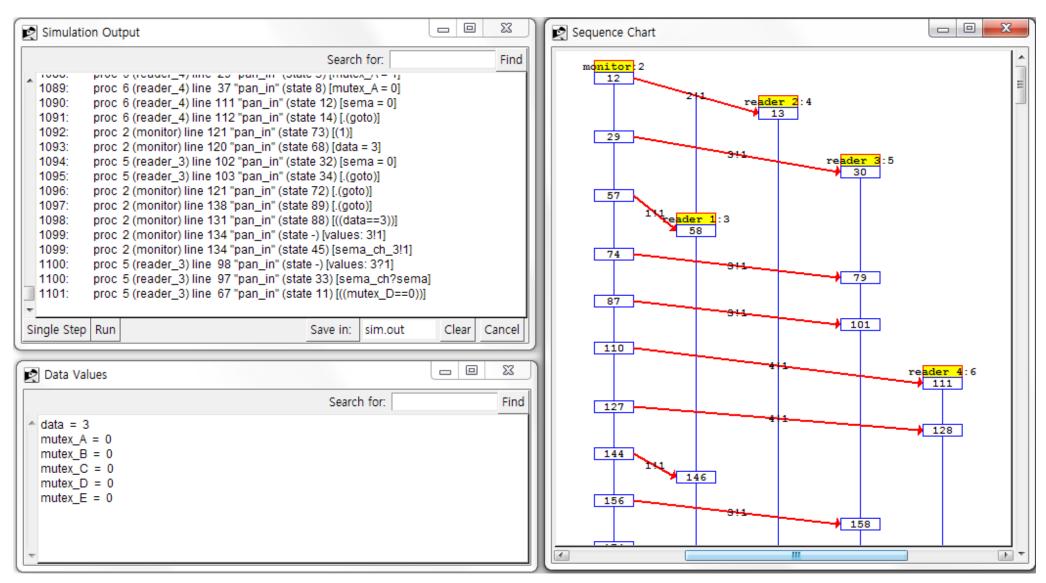

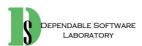

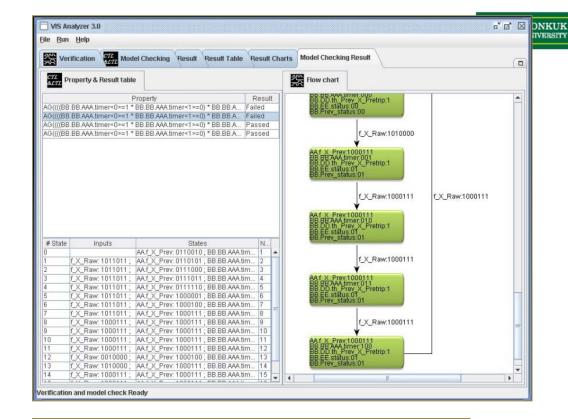

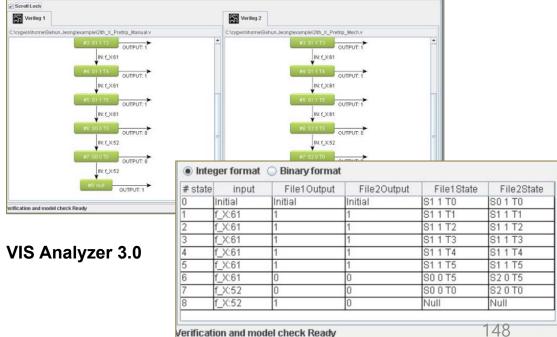

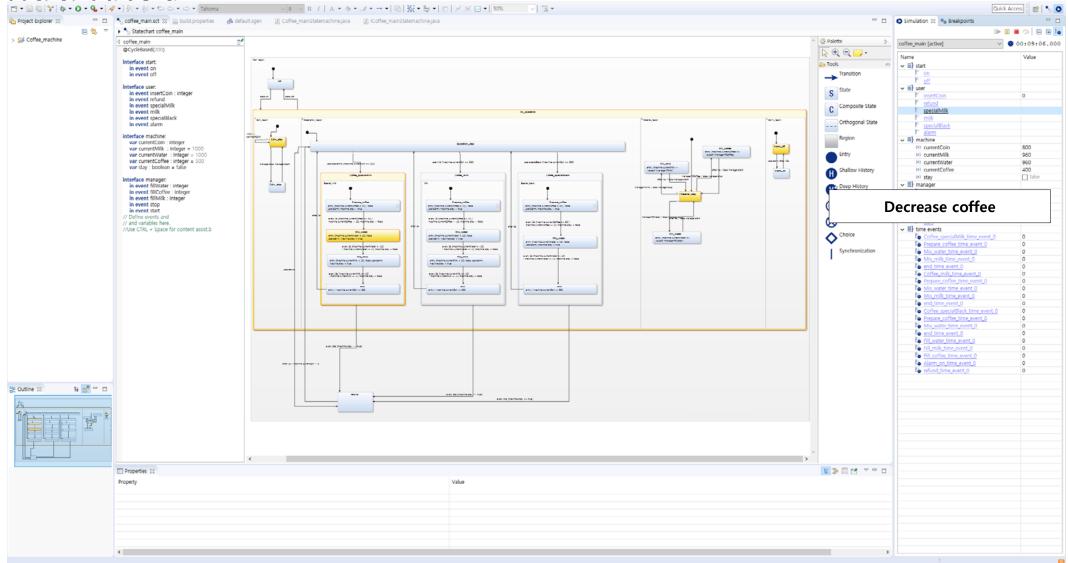

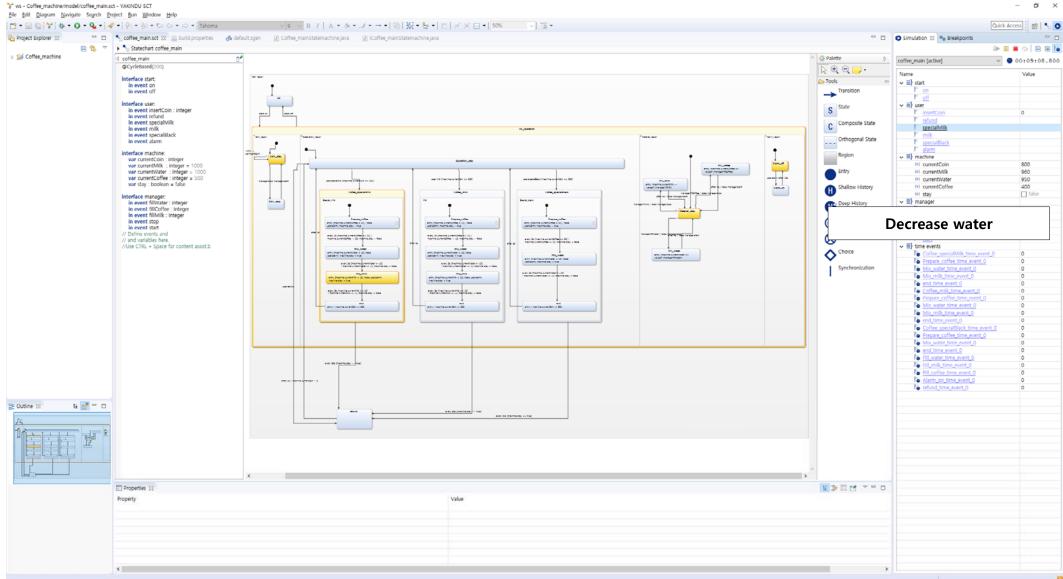

| A[] !(Ctr, Wait4 && Ctr, clk > t20ms && Reader2, Write4)<br>Property is not satisfied,<br>A[] !(Ctr, Wait3 && Ctr, clk > t20ms && Reader2, Write3)<br>Property is not satisfied,<br>A[] !((Ctr, Wait2_0    Ctr, Wait2_1) && Ctr, clk > t20ms && (Reader0, Write1    Reader1, Write1    R<br>Property is not satisfied,<br>A[] !(Ctr, Wait1 && Ctr, clk > t20ms && (Reader0, Write1    Reader1, Write1    R                                                                                                                                                                                                         | leader2, Write2           |