# Getting started with SMV

K. L. McMillan Cadence Berkeley Labs 2001 Addison St. Berkeley, CA 94704 USA mcmillan@cadence.com

March 23, 1999

# cādence

#### Abstract

This tutorial introduces the SMV verification system. It includes examples of temporal logic model checking, and refinement verification, including techniques of circular compositional proof, temporal case splitting, symmetry reduction, data type reduction and induction.

©1998 Cadence Berkeley Labs, Cadence Design Systems.

# 1 Introduction

This is a short tutorial introduction to SMV, a verification system for hardware designs. SMV is a formal verification tool, which means that when you write a specification for a given system, it verifies that every possible behavior of the system satisfies the specification. This is in contrast to a simulator, which can only verify the system's behavior for the particular stimulus that you provide.

A specification for SMV is a collection of properties. A property can be as simple as a statement that a particular pair of signals are never asserted at the same time, or it might state some complex relationship in the values or timing of the signals. Properties are specified in a notation called *temporal logic*. This allows concise specifications about temporal relationships between signals. Temporal logic specifications about finite state systems can be automatically formally verified by a technique called *model checking*.

SMV is quite effective in automatically verifying properties of combinational logic and interacting finite state machines. Sometimes, when checking properties of complex control logic, the verifier will produce a counterexample. This is a behavioral trace that violates the specified property. This makes SMV a very effective debugging tool, as well as a formal verification system.

Model checking by itself is limited to fairly small designs, because it must search every possible state that a system can reach. For large designs, especially those including substantial data path components, the user must break the correctness proof down into parts small enough for SMV to verify. This is known as *compositional* verification. SMV provides a number of tools to help the user reduce the verification of large, complex systems to small finite state problems. These techniques include *refinement verification*, symmetry reduction, temporal case splitting, data type reduction, and induction.

This tutorial will introduce all of the above techniques by example.

# 2 Modeling, specifying and verifying

We will start with some very simple examples, to illustrate the process of entering a model, specifying properties, and running SMV to verifying them. You can enter the examples yourself, using a text editor (and thus become acquainted with SMV's response to syntax errors). Or, if you are reading this tutorial on-line, you can follow the hyperlinks to the corresponding files.

Consider, for example, the following description of a very simple combinational circuit, with some assertions added. This example is written in SMV's native language. Use a text editor to enter the following program into a file called "prio.smv".

```

module main(req1,req2,ack1,ack2)

{

input req1,req2 : boolean;

output ack1,ack2 : boolean;

ack1 := req1;

ack2 := req2 & ~req1;

```

```

mutex : assert ~(ack1 & ack2);

serve : assert (req1 | req2) -> (ack1 | ack2);

waste1 : assert ack1 -> req1;

waste2 : assert ack2 -> req2;

}

```

This example shows most of the basic elements of an SMV module. The module has four *parameters*, req1, req2, ack1 and ack2, of which the former two are inputs, and the latter two outputs. It contains:

- Type declarations. In this case the signals req1, req2, ack1 and ack2 are declared to be of type boolean.

- Signal assignments. These give logic functions for outputs ack1 and ack2 in terms of inputs req1 and req2.

- Assertions. These are properties to be proved.

The program models a (highly trivial) two bit priority-based arbiter, which could be implemented with a two-gate circuit. The assert statements specify a number of properties that we would like to prove about this circuit. For example, the property called mutex says that outputs ack1 and ack2 are not true at the same time. Note that & stands for logical "and" while ~ stands for logicol "not". The property serve says that if either input req1 or req2 is true, then one of the two outputs ack1 or ack2 is true. Note that | stands for logical "or", while -> stands for "implies". Logically, a -> b is equivalent to ~a | b, and can be read "a implies b" or "if a then b".

We would like to verify these specifications formally, that is, for all possible input patterns (of which in this case there are only four). To do this under Unix, enter the following shell command:

#### vw prio.smv

On a PC under Windows, double-click the icon for the file "prio.smv". This will start the SMV viewer, called "vw", with the file "prio.smv". This interface has a number of tabbed pages, which can be accessed by clicking an the appropriate tab. When you start the interface, you see the browser, which is a tree representation of all the signals and assertions in your source file, and the source page, which shows the source file. If you made a syntax error in the source file, this error will be pointed out on the source page. Correct the error, and then choose "Reopen" from the "File" menu.

If you have no syntax errors, expand top level in the browser by double-clicking it, or by clicking the + icon. The + indicates that top level has children which are not currently visible. You should see under top level the names of all the signals and properties in your source file. Since none of these has children, they will not be marked with a +. Select one of these, and notice the highlight in the source page moves to the location in the program where that signal or property is declared. Select the signal ack2, and then in the source page, select "Where assigned" in the "Show" menu. The souce line where ack2 is assigned will now be highlighted.

Now select "Verify all" from the "Prop" menu. SMV verifies the four properties in our program. The results page now shows the results of this verification run. In this case, all the properties are true.

Now let's modify the design so that one of the specifications is false. For example, change the line

ack1 := req1;

$\operatorname{to}$

ack1 := req1 & ~req2;

Save the modified text file and choose "Reopen" from the "File" menu (or, if you are on-line, just click here to save typing). Then select "Prop—Verify all" again. Notice that this time the property **serve** is false. Also note, not all of the properties appear in the results pane. This is because SMV stops when it reaches the first property that is false. Thus, not all the properties were checked.

When a property is false, SMV produces a counterexample that shows a case when it doesn't hold. To see the counterexample for **serve**, select it in the results page by clicking on it. The trace page will appear, showing a counterexample – a truth assignment to all the signals that shows that our property is false. The counterexample shows the case when both inputs are true and both outputs are false.

The verifier keeps track of which properties have been verified since the most recent source file change. You can see which properties have been verified thus far, by selecting the properties page. Currently only **mutex** is verified. To verify **waste1**, for example, click on it in the properties page, and then choose "Verify waste1" from the "Prop" menu. Notice that only the property you select is verified in this case. The name of the property that is currently selected appears at the bottom of the window.

#### 2.1 Sequential circuits and temporal properties

To specify sequential circuits, we need to be able to make statements about how signals evolve over time. SMV uses a notation called *temporal logic* for this purpose. Temporal logic formulas are like formulas in ordinary boolean logic, except that truth value of a formula in temporal logic is a function of time. Some new operators are added to the traditional boolean operators "and", "or", "not" and "implies", in order to specify relationships in time.

For example, the F operator is used to express a condition that must hold true at some time in the future. The formula F p is true at a given time if p is true at some later time. On the other hand, G p means that p is true at all times in the future. Usually, we read F p as "eventually p" and G p as "henceforth p".

In addition, we have the "until" operator and the "next time" operator. The formula p U q, which is read "p until q" means that q is eventually true, and until then, p must always be true. The formula X p means that p is true at the next time.

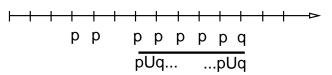

Here are the exact definitions of the temporal logic operators, with example time lines showing the states when they hold true: • The "globally" operator: **G p** is true at time t if **p** is true at all  $t' \ge t$ .

- The "until" operator: p U q is true at time t iff

- $\mathbf{q}$  is true at some  $t' \geq t$ , and

- p is true in the range [t, t')

• The "next time" operator: **X p** is true at time t if **p** is true at time t + 1.

As an example, suppose we are designing a bus arbiter with two "grant" signals, ack1 and ack2. Among other things, we want to specify that the two grant signals are never asserted at the same time. In temporal logic, we would write G ~(ack1 & ack2). The G operator is used to say that our specification should hold true at all times. This is needed because SMV interprets "assert" statements to hold at the initial state of execution of the program. If we wrote only ~(ack1 \& ack2), SMV would interpret this only to mean that both grants may not be asserted at time t = 0.

Return to our original example, and edit the four properties we specified so that they begin with the G operator. Make sure to undo the error we introduced in the previous section. You should have something like this:

```

module main(req1,req2,ack1,ack2)

{

input req1,req2 : boolean;

output ack1,ack2 : boolean;

ack1 := req1;

ack2 := req2 & ~req1;

mutex : assert G ~(ack1 & ack2);

serve : assert G ((req1 | req2) -> (ack1 | ack2));

waste1 : assert G (ack1 -> req1);

```

```

waste2 : assert G (ack2 -> req2);

}

```

Open the file and choose "Prop—Verify all" again to confirm that the properties we specified in fact hold true for all time. This is because the two logic equations we wrote for ack1 and ack2 hold implicitly for all time. Now let's write a more interesting temporal specification. Suppose we want to use our priority circuit as a bus arbiter. In addition to the above properties, we would like to avoid "starvation" of the low priority requester. That is, we don't want req2 to be asserted forever while ack2 is never asserted. Put another way, we want it to always eventually be true that either req2 is negated or ack2 is asserted. In temporal logic, we write "always eventually" by combining G and F. In this case we assert: G F ("req2 | ack2). Therefore, add the following specification to the program:

```

no_starve : assert G F (~req2 | ack2);

```

Now open the new version and verify the property no\_starve. The property should be false, and a counterexample trace with one state should appear in the trace page. Notice that the state number is marked with "repeat" signs, thus: |: 1 :|. This is to indicate that the first state repeats forever. In this state, both req1 and req2 are asserted. Since req1 has priority, ack2 is never asserted, hence requester 2 "starves".

As an aside, you might also have observed that the signal ack1 doesn't appear in the trace. This is because SMV noticed that the property no\_starve doesn't actually depend on this signal, so it left ack1 out of its analysis. The set of signals that a property depends on is referred to as the *cone* of that property. When you have selected a given property to verify, you can view the cone of that property by clicking the "Cone" tab. In this case, you'll notice that the signals req1 and req2 are listed as "free". This is because they are unconstrained inputs to the circuit, and thus are free to take on any values in their type. These signals each contribute one "combinational" variable to the verification problem. SMV must verify the property you specified for all possible combinations of these variables. Thus, it is generally best to keep the number of variables in the cone small, when possible.

Now, to prevent this starvation case, let's add a latch to the circuit that remembers whether ack1 was asserted on the previous cycle. In this case we'll give priority to requester 2 instead. To do this, add the following code to the program:

```

bit : boolean;

next(bit) := ack1;

```

The above means that **bit** is a boolean variable, and that the value of **bit** at time t + 1 is equal to the value of **ack1** at time t. This is how a state variable (or a register, if you like) is represented to SMV – as an equation involving one time unit of delay. Now, replace the definitions of **ack1** and **ack2** with the following:

```

if (bit) {

ack1 := req1 & ~req2;

ack2 := req2;

}

```

```

else {

ack1 := req1;

ack2 := req2 & ~req1;

}

```

That is, when bit is set, we reverse the priority order. Note that even though this may look like a sequential program, it really represents two simultaneous equations. If you like, you can write the same thing instead like this:

```

ack1 := bit ? req1 & ~req2 : req1;

ack2 := bit ? req2 : req2 & ~req1;

```

Now open the new version and verify property no\_starve. It should be true. By the way, you might have noticed that we didn't specify an initial (*i.e.* reset) value for the register bit. In fact, SMV verified no\_starve for both possible initial values. If you check the "Cone" panel, you'll notice that there are now two combinational variables (the inputs) and one state variable (the signal bit).

# 2.2 A three-way arbiter

Now let's try to apply the same idea to a three-way bus arbiter. In this version, we will have one latched bit for each requester. This bit holds a one when the corresponding requester was granted the bus on the previous cycle. We'll still use a fixed priority scheme, but if a given request was granted on the previous cycle, we'll give it lowest priority on the current cycle. Thus, if the bit for a given requester is set, its request is served only if no others are requesting. Further, the requester with its bit set does not inhibit lower priority requesters. Here is one attempt at such an arbiter:

The specifications for the three-way arbiter are as follows:

```

mutex : assert G ~(ack1 & ack2 | ack1 & ack3 | ack2 & ack3);

serve : assert G ((req1 | req2 | req3) -> (ack1 | ack2 | ack3));

waste1 : assert G (ack1 -> req1);

waste2 : assert G (ack2 -> req2);

waste3 : assert G (ack3 -> req3);

no_starve1 : assert G F (~req1 | ack1);

no_starve2 : assert G F (~req2 | ack2);

no_starve3 : assert G F (~req3 | ack3);

```

They are similar to the two-way case, but note that in mutex we consider all pairs. Also, we've specified non-starvation for all of the requesters, just in case. Save this program in a file (you can put the specifications anywhere inside the module declaration – statement order is irrelevant in SMV). Then open the file and choose "Verify all". You should get a false result for no\_starve3. Click on no\_starve3 and observe the counterexample trace. This is an example of a "livelock". The last two states in the counterexample repeat forever. Notice that requesters 1 and 2 are served alternately while requester 3 starves.

In fact, there is another error in the design. If you select the **serve** property and try to verify it, you'll find that **serve** can be false in the initial state. This occurs if more than one of the **bits** are true initially. We could rule this out by specifying initial values for these bits, as follows:

```

init(bit1) := 0;

init(bit2) := 0;

init(bit3) := 0;

```

Alternatively, if we don't care if no one gets served in the initial state, we can change the specification. In temporal logic X p means that p is true at the "next" time. Thus, for example X G p means that p holds from the second state onward. Thus, we could change the specification to:

```

serve : assert X G ((req1 | req2 | req3) -> (ack1 | ack2 | ack3));

```

As an exercise, you might want to try designing and verifying a three-way arbiter that satisfies all the specifications above.

## 2.3 A traffic light controller

Now we'll consider a slightly more complex example that uses some additional features of SMV's language. The example is a controller that operates the traffic lights at an intersection where two-way street running north and south intersects a one-way street running east. The goals are to design the controller so that collisions are avoided, and no traffic waits at a red light forever.

The controller has three traffic sensor inputs, N\_Sense, S\_Sense and E\_Sense, indicating when a car is present at the intersection traveling in the north, south and east directions respectively. There are three outputs, N\_Go, S\_Go and E\_Go, indicating that a green light should be given to traffic in each of the three directions.

```

module main(N_Sense,S_Sense,E_Sense,N_Go,S_Go,E_Go){

input N_Sense,S_Sense,E_Sense : boolean;

output N_Go,S_Go,E_Go : boolean;

```

In addition, there are four internal registers. The register NS\_Lock is set when traffic is enabled in the north or south directions, and prevents east-going traffic from being enabled. The three bits N\_Req, S\_Req, E\_Req are used to latch the traffic sensor inputs.

NS\_Lock, N\_Req, S\_Req, E\_Req : boolean;

The registers are initialized as follows:

```

init(N_Go) := 0;

init(S_Go) := 0;

init(E_Go) := 0;

init(NS_Lock) := 0;

init(N_Req) := 0;

init(S_Req) := 0;

init(E_Req) := 0;

```

In modeling the traffic light controller's behavior, we will use two new SMV statements. The **case** statement is a conditional form. The sequence:

```

case{

cond1 : {block1}

cond2 : {block2}

cond3 : {block3}

}

```

is equivalent to

if (cond1) {block1}

else if (cond2) {block2}

else if (cond3) {block3}

In addition, we will use the **default** construct to indicate that certain assignments are to be used as defaults when the given signals are not assigned in the code that follows. In a sequence like this:

```

default {block1}

in {block2}

```

assignments in block2 take precedence over assignments in block1. SMV enforces a "single assignment rule", meaning that only one assignment to a given signal can be active at any time. Thus, if we have more than one assignment to a signal, we must indicate which of the two takes precedence in case both apply.

Now, returning to the traffic controller, if any of the sense bits are true, we set the corresponding request bit:

```

default{

if(N_Sense) next(N_Req) := 1;

if(S_Sense) next(S_Req) := 1;

if(E_Sense) next(E_Req) := 1;

}

```

The code to operate the north-going light is then as follows:

```

in default case{

N_Req & ~N_Go & ~E_Req : {

next(NS_Lock) := 1;

next(N_Go) := 1;

}

N_Go & ~N_Sense : {

next(N_Go) := 0;

next(N_Req) := 0;

if(~S_Go) next(NS_Lock) := 0;

}

}

```

This says that if a north request is latched, and the north light is not green and there is no east request, then switch on the north light and set the lock (in effect, we give priority to the east traffic). If the north light is on, and there is no more north traffic, switch off the light, clear the request, and switch off the lock. Note however, that if the south light is on, we don't switch the lock off. This is to prevent south and east traffic from colliding. The south light code is similar:

```

in default case{

S_Req & ~S_Go & ~E_Req : {

next(NS_Lock) := 1;

next(S_Go) := 1;

}

S_Go & ~S_Sense : {

next(S_Go) := 0;

next(S_Req) := 0;

if(~N_Go) next(NS_Lock) := 0;

}

}

```

Finally, the east light is switched on whenever there is an east request, and the lock is off. When the east sense input goes off, we switch off the east light and reset the request bit:

```

in case{

E_Req & ~NS_Lock & ~E_Go : next(E_Go) := 1;

E_Go & ~E_Sense : {

next(E_Go) := 0;

next(E_Req) := 0;

```

} }

There are two kinds of specification we would like to make about the traffic light controller. The first is a "safety" specification that say that lights in cross directions are never on at the same time:

safety: assert G ~(E\_Go & (N\_Go | S\_Go));

The second is a "liveness" specification, for each direction, which says that is the traffic sensor is on for a given direction, then the corresponding light is eventually on, thus no traffic waits forever at a read light:

```

N_live: assert G (N_Sense -> F N_Go);

S_live: assert G (S_Sense -> F S_Go);

E_live: assert G (E_Sense -> F E_Go);

```

Note, however, that our traffic light controller is designed so that it depends on drivers not waiting forever at a green light. We want to verify the above properties given that this assumption holds. To do this, we write some "fairness constraints", as follows:

```

N_fair: assert G F ~(N_Sense & N_Go);

S_fair: assert G F ~(S_Sense & S_Go);

E_fair: assert G F ~(E_Sense & E_Go);

```

Each of these assertions states that, always eventually, it is not the case that a car is at a green light. To tell SMV to assume these "fairness" properties when proving the "liveness" properties, we say:

```

using N_fair, S_fair, E_fair prove N_live, S_live, E_live;

assume E_fair, S_fair, N_fair;

}

```

Because of the **assume** statement, the fairness constraints themselves will simply be left unproved. Now, open this file and try to verify the property **safety**. The result should be "false", and in the "Trace" panel, you should see a counterexample trace in which the south light goes off exactly at the time when the north light goes on. The result is that the lock bit is cleared. This is because the code for the south light takes precedence over the code for the north light, due to our use of **default**. With the north light on and the lock cleared, the east light can now go on, violating the safety property.

To fix this problem, let's change the south light code so that it tests to see whether that north light is about to go on before clearing the lock. Here is the revised code for the south light:

```

in default case{

S_Req & ~S_Go & ~E_Req : {

next(NS_Lock) := 1;

next(S_Go) := 1;

```

```

}

}

S_Go & ~S_Sense : {

next(S_Go) := 0;

next(S_Req) := 0;

if(~(N_Go | N_Req & ~N_Go & ~E_Req)) next(NS_Lock) := 0;

}

```

Open this new version and verify the property safety. It should be true. Now try to verify N\_live. It should come up false, with a counterexample showing a case where both the north and south lights are going off at exactly the same time. In this case neither the north code nor the south code clears the lock, because each thinks that the other light is still on. As a result, the lock remains on, which prevents an east request from being served. Since the east request takes priority over north and south requests, the controller is deadlocked, and remains in the same state indefinitely (note the "repeat signs" on the last state).

To fix this problem, we'll give the north light controller the responsibility to turn off the lock when both lights are going off. Here's the new north light code:

```

in default case{

N_Req & ~N_Go & ~E_Req : {

next(NS_Lock) := 1;

next(N_Go) := 1;

}

N_Go & ~N_Sense : {

next(N_Go) := 0;

next(N_Req) := 0;

if(~S_Go | ~S_Sense) next(NS_Lock) := 0;

}

}

```

Open this new version and verify the properties safety, N\_live, S\_live and E\_live. They should all be true. Note that if you try to verify the fairness constraints N\_fair, S\_fair and E\_fair, they will come up false. These are unprovable assumptions that we made in designing the controller. However, if we used the controller module in a larger circuit, we could (and should) verify that the environment we put the controller into actually satisfies these properties. In general, it's best to avoid unproved assumptions if possible, since if any of these assumptions is actually false, all the properties we "proved" are invalid.

# 3 Symbolic model checking

A model checker verifies a property by building a graph of all of the states in the model. In SMV, the number of states in the model is  $2^n$ , where *n* is the number of state variables in the cone of the property. In fact, it is only necessary for the model checker to consider the states that are "reachable" from an initial state. However, as you might expect, the amount of computational effort required to verify a property still tends to grow very rapidly with the number of state variables. This is known as the "state explosion problem".

To address this problem, SMV uses a structure called a "Binary Decision Diagram" (BDD) to implicitly represent the state graph of the model, and sets of states satisfying given properties. For some models and properties, the use of BDD's (implicit enumeration) allows SMV to handle models with many orders of magnitude more states than could be handled by considering individual states (explicit enumeration). First, we see a simple example of a circuit with a very large number of states that can still be handled efficiently using BDD's. Later we'll consider what to do when a direct approach using BDD's doesn't work.

# **3.1** A buffer allocation controller

This example is designed to control the allocation and freeing of buffers in, for example, a packet router. The controller keeps an array of "busy" bits, one for each available data buffer. The busy bit is true when the buffer is in use, and false otherwise. An input alloc indicates a request to allocate a new buffer for use. If there is a buffer available, the controller outputs the index of this buffer on a signal alloc\_addr. If there is no buffer available, it asserts an output nack. To make the circuit a little more interesting, we'll add a counter that keeps track of the number of busy bits that are set. Thus nack is asserted when the count is equal to the total number of buffers. To begin with, we'll define the number of buffers to be 32, using a C-style macro definition:

```

#define SIZE 32

module main(alloc,nack,alloc_addr,free,free_addr)

{

input alloc : boolean;

output nack : boolean;

output alloc_addr : 0..(SIZE - 1);

input free : boolean;

input free_addr : 0..(SIZE - 1);

busy : array 0..(SIZE - 1) of boolean;

count : 0..(SIZE);

init(busy) := [0 : i = 0..(SIZE-1)];

init(count) := 0;

```

Note that we initialized **busy** to a vector of 32 zeros using an iterator expression. Here is the logic for the counter and the **nack** signal. Notice, we add one to the counter when there is an allocation request and **nack** is not asserted. We subtract one from the counter when there is a free request, and the buffer being freed is actually busy. Note, if we didn't check to see that the freed buffer is actually busy, the counter could get out of sync with the busy bits.

```

nack := alloc & (count = SIZE);

next(count) := count + (alloc & ~nack) - (free & busy[free_addr]);

```

Next we handle the setting and clearing of the busy bits. We use a default statement to indicate that, if a given buffer is being both freed and allocated at the same time, the allocation request takes precedence.

```

default{

if(free) next(busy[free_addr]) := 0;

} in {

if(alloc & ~nack) next(busy[alloc_addr]) := 1;

}

```

Finally, we choose a buffer to allocate using a priority encoder. This is most easily generated using the **chain** constructor. This repeats a given block of statements for a range of index values, given precedence to later iterations. So, for example

chain (i = 0; i < 3; i = i + 1) block(i)

is equivalent to

```

default block(0) in default block(1) in default block(2)

```

Our priority encoder is defined as follows:

```

chain(i = (SIZE - 1); i >= 0; i = i - 1){

if(~busy[i]) alloc_addr := i;

}

```

Since the last statement in the chain is the case i = 0, we effectively give highest priority to buffer 0. Note, in the case when all buffers are busy, alloc\_addr in not assigned, and thus remains undefined.

Now, we consider the problem of specifying the buffer allocator. We will write a separate specification for each buffer, stating that the given buffer is never allocated twice without being freed in the interim. This is a technique known as "decomposition", that is, breaking a complex specification of a system into smaller parts that can be verified separately. To make it simpler to state the specification, it helps to define some additional signals: a bit allocd[i] to indicate that buffer i is currently being allocated, and a bit freed[i] to indicate that buffer i is currently being freed:

```

for(i = 0; i < SIZE; i = i +1){

allocd[i], freed[i] : boolean;

allocd[i] := alloc & ~nack & alloc_addr = i;

freed[i] := free & free_addr = i;

}</pre>

```

Note, we used a for constructor to make an instance of these definitions for each buffer i. To write the specification that a buffer is not allocated twice, we can use "until" operator of temporal logic. Recall that the formula p U q in temporal logic means that q is eventually true, and until then, p must always be true.

```

for(i = 0; i < SIZE; i = i +1){

safe[i] : assert G (allocd[i] -> ~ X ((~freed[i]) U allocd[i]));

}

}

```

Here we state that, if buffer i is allocated, then it is not the case that, starting at the next time, it remains unfreed until it is allocated a second time.

Now, let's verify this specification. Open the file and verify the property safety[0]. This should take something under a minute. If you watch the log output during the verification process, you'll notice that it is reporting a sequence of "iterations". These are the steps of a breadth-first search of the model's state space, starting from the initial states. The numbers reported are the sizes of the BDD's representing the set of states reached thus far in the search. The size of the BDD's can be much smaller than the number of states in the set. To see this, select "Prop—State count". This will rerun the verification and report the number of states reached at each iteration. The final number of states reached in this case is something over two billion.

Now let's increase the number of buffers from 32 to 64. Change the definition of SIZE at the beginning of the program to

#### #define SIZE 64

Open the new version, select the property safety[0], and then select "Prop—State count". This will verify the property, and also compute the number of states reached. You might want to go make a cup of coffee at this point, since the computation will take ten or twenty minutes. The only point to be made here is that the number of states reached is on the order of  $10^{19}$ , while the BDD representing this set of state has about 4000 "nodes". This shows that the BDD's can be a very compact representation for large sate sets. Sometimes, this makes it possible to verify a model, even though the number of states is much too large to be searched "explicitly" (*i.e.* larger than the number of atoms in the universe).

There is no guarantee, however, that SMV's BDD-based algorithms will be able solve a given verification problem. This is because the problem is SMV is trying to solve is fundamentally hard (PSPACE complete, to be precise). On the other hand, when SMV fails to solve a verification problem (or when we run out of patience waiting for it to solve the problem), there are usually many ways to make the problem simpler for SMV to solve. This usually involves decomposition – breaking big problems into small problems, and then localizing the verification of each subproblem to a small part of the overall model. This technique is described in the following section.

# 4 Refinement verification

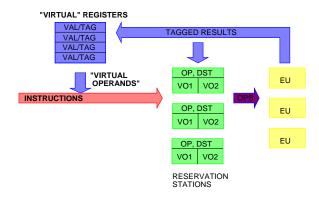

Refinement verification is methodology of verifying that the functionality of an abstract system model is correctly implemented by a low-level implementation. It can be used, for example, to verify that a packet router or bus protocol, modeled at the clock-cycle level, correctly implements a given abstract model of end-to-end data transfer. Similarly one can verify that a clock-accurate model of a pipelined, out-of-order processor correctly implements a given instruct-set architecture (*i.e.*, a programmer's model of a machine).

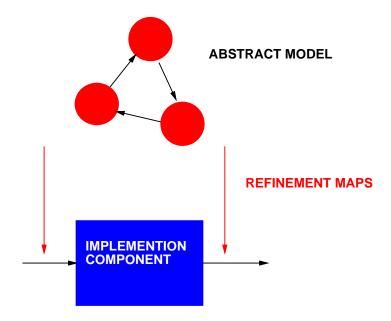

By breaking a large verification problem into small, manageable parts, the refinement methodology makes it possible to verify designs that are much too large to be handled directly by model checking. This decomposition of the verification problem is enabled by specifying *refinement maps* that translate the behavior of the abstract model into the behavior of given

Figure 1: Refinement maps

interfaces and structures in the low-level design. This makes it possible to verify small parts of the low-level design in the context of the abstract model. Thus, the proof obligations can be reduced to a small enough scale to be verified by model checking.

SMV supports this methodology by allowing one to specify many abstract definitions for the same signal. A new construct called a "layer" is introduced for this purpose. A layer is a collection of abstract signal definitions. A layer can, for example, define low-level implementation signals as a function of abstract model signals, and thus provide a refinement map (*i.e.*, a translation between abstraction levels). The low-level implementation of a signal must be simultaneously consistent with all of its abstract definitions. Thus, each abstract definition entails a verification task – to show that every implementation behavior is allowed by this definition. For the purpose of this verification task, one may use whichever abstract definition is most convenient for defining of the other signals. Suppose, for example, that we have abstract definitions of both the inputs and outputs of a given low-level block as a function of a high-level model, as depicted in figure 1. We can use the abstract definitions of the inputs to drive the inputs of the block from the high-level model when verifying that the outputs are consistent with their abstract definitions. Thus, the abstract model provides the context (or environment) for verifying the block, and we do not need to consider the remainder of the low-level model.

SMV also supports design by a successive refinement. One can define a sequence of layers, each of which is more detailed than the previous layer. The implementation of each signal is given by the lowest-level definition in the hierarchy.

#### 4.1 Layers

A layer is a collection of abstract signal definitions. These are expressed as assignments in exactly the same way that the implementation is defined, except that they are bracketed by

```

a layer statement, as follows:

layer <layer_name> : {

assignment1;

assignment2;

...

assignmentn;

}

```

where each assignment is of the form

<signal> := <expression>;

or

```

next(<signal>) := <expression>;

```

or

```

init(<signal>) := <expression>;

```

High level control structures, such as if, switch and for can also be used inside a layer construct, since these are simply "syntactic sugar" for assignments of the above form.

The layer declaration is actually a formal specification, which states that every implementation behavior must be consistent with all of the given assignments. If this is the case, we say the implementation refines the specification.

As an example, let's consider a very simple example of a specification and implementation of a finite state machine:

```

module main(){

x : boolean;

/* the specification */

layer spec: {

init(x) := 0;

if(x=0) next(x) := 1;

else next(x) := {0,1};

}

/* the implementation */

init(x) := 0;

next(x) := ~x;

}

```

Note that spec is not a keyword here – it is just an arbitrary name given to our specification. This specification is nondeterministic, in that at state 1, it may transition to either state 0 or state 1. The implementation on the other hand has only one behavior, which alternates between state 0 and state 1. Since this is one possible behavior of spec, the specification spec is satisfied.

If you enter this example into a file, and open the file with vw, you will find in the Properties page a single entry named x//spec. This is a notation for "the definition of signal x in layer spec". It appears in the Properties page because it is an obligation to be verified, rather than a part of the implementation. You can verify it by selecting "Prop—Verify all". SMV does this by translating the assignment into an initial condition and transition invariant. The former states that x is 0 at time t = 0, while the latter states that the value of x at time t + 1 is 1 if x is 0 at time t, and else is either 0 or 1. The implementation must satisfy these two conditions, which are verified by exhaustive search of the state space of the implementation.

If more than one signal is assigned in a layer, then the two definitions are verified separately. This is known as **decomposition**. The reason for using decomposition is that we may be able to use a different abstraction of the implementation to prove each component of the specification. As a very simple example, consider the following program:

```

module main(){

x,y : boolean;

/* the specification */

layer spec: {

x := 1;

y := 1;

}

/* the implementation */

init(x) := 1;

next(x) := y;

init(y) := 1;

next(y) := x;

}

```

Both state bits in the implementation start at 1, and at each time they swap values. Thus, the specification is easily seen to be satisfied – both x and y are always equal to 1. If you open this example with vw, you will find two entries in the Properties page: x//spec and y//spec. Each of these can be verified separately (i.e., we can verify separately that x is always equal to 1 and that y is always equal to 1). Suppose we want to verify x//spec (select it in the Properties page). We now have two choices: we can use either the specification definition of y or the implementation definition y. Note, however, that if we use the specification definition of y, we eliminate one state variable from the model, since y is defined to be identically 1.

Thus, by decomposing a specification into parts, and using one part as the "environment" for another, we have reduced the number of state variables in the model, and thus reduced the verification cost (though it is in any event trivial in this case). In fact, if you click on the Cone tab in vw, you will see that SMV has selected layer **spec** to define **y**, and that as a result, **y** is not a state variable. This is because SMV assumes by default that it is better to use an abstract definition of a signal than a detailed one. Select "Prop—Verify **x**//spec" to verify the property using this abstraction.

Note that y//spec can now be verified using x//spec to define x. This might at first seem to be a circular argument. However, SMV avoids the potential circularity by only assuming y//spec holds up to time t - 1 when verifying x//spec at time t, and vice versa. Because of this behavior, we need not be concerned about circularities when choosing an abstract definition to drive a signal. SMV does the bookkeeping to insure that when all components of the specification are declared "verified", then in fact the implementation refines the specification.

# 4.2 Refinement maps

The most effective way to decompose the specification and verification of a system into manageable parts is to define an abstract model as a specification, and then to specify "refinement maps" that relate abstract model behaviors to implementation behaviors. Generally, abstract models specify "what" is being done, without specifying the "how", "where" or "when". The "where" and "when" are given by the refinement maps, while the implementation determines the "how". In the simplest case the abstract model does nothing at all. For example, in the case of a link-layer protocol that simply transfers a stream of data from point A to point B without modifying it, there is no "what" and the only important information is the "where" and "when". The abstract model in this case might consist only of the stream of data itself. In the case of a microprocessor, the abstract model might determine the sequence of instructions that are executed according to the ISA (instruction set architecture). The refinement map would determine what instruction appears at each stage of the pipeline at any given time.

#### 4.2.1 A very simple example

We will consider first a very simple example of specifying abstractions and refinement maps. Suppose that we would like to design a circuit to transmit an array of 32 bytes from its input to its output, without modifying the array. The abstract model in this case is just an unchanging array of bytes, since no actual operations are performed on the array. The refinement maps specify the protocol by which the array is transferred at the input and output. We'll assume the the input consists of three components: a bit valid indication the the input currently holds valid data, an index idx that tells which element of the array is currently being transferred, and a byte data that gives the value of this element. Assume the output uses a similar protocol. Thus far, we have the following specification:

typedef BIT 0..7; typedef INDEX 0..31;

```

typedef BYTE array BIT of boolean;

module main(){

/* the abstract model */

bytes : array INDEX of BYTE;

next(bytes) := bytes;

/* the input and output signals */

inp, out : struct{

valid : boolean;

idx : INDEX;

data : BYTE;

}

/* the refinement maps */

layer spec: {

if(inp.valid) inp.data := bytes[inp.idx];

if(out.valid) out.data := bytes[out.idx];

}

```

Note that the abstract model simply states that nothing happens to the array of bytes. The refinement map is partially specified. For example, if inp.valid is 0, then inp.data is allowed to have any value, since there is no else clause in the conditional. You can think of this as a "don't care" case in the specification.

Now let's add a very trivial implementation:

```

init(out.valid) := 0;

next(out) := inp;

}

```

That is, the output is just the input delayed by one time unit. Note, at time t = 0 we have to signal that the output is not valid, but we don't have to specify initial values for idx and data since they are "don't cares" in this case.

Save this program in a file and open it with vw. Note that there are eight properties in the file, of the form out.data[i]//spec, where i = 0..7. Select property out.data[0]//spec, for example. If you click on the Cone tab, you'll notice that only signals with bit index 0 appear. This is because SMV has detected the property you selected doesn't depend on the other bit indices. Also notice that the data input signal inp.data[0] has used layer spec for its definition (since this is in fact the only available definition at this point). Thus, we are driving the input of our implementation from the abstract model (again through a refinement map) and verifying the output with respect to the abstract model (again through a refinement map). Now, select "Prop—Verify out.data[0]//spec". It should take less than 2 seconds

to verify this property. You can select "Prop—Verify All" to verify the remainder of the refinement maps. SMV will quickly recognize that the 7 remaining verification problems are isomorphic to the one we just solved, and report "true" for all of them. Note that although we have reduced the number of state bits by a factor of eight by using decomposition (since we only deal with one bit index at a time) we are still using 32 bits out of the data array for each verification. This gives us 39 state bits, which is a fairly large number and guarantees us at least 4 billion states. In this case, the large state space is easily handled by the BDD-based model checker, so we do not have to do any further decomposition. In general however, we cannot rely on this effect. Later we'll see how to decompose the problem further, so that we only use one bit from the data array.

## 4.2.2 End-to-end verification

Now we'll consider a more complex (though still trivial) implementation with multiple stages of delay. The goal is to verify the end-to-end delivery of data by considering each stage in turn, specifying a refinement map for each stage. The refinement map for each stage drives the input of the next. Suppose we replace the above implementation with the following implementation that has three time units of delay:

```

stage1, stage2 : struct{

valid : boolean;

idx : INDEX;

data : BYTE;

}

init(stage1.valid) := 0;

next(stage1) := inp;

init(stage2.valid) := 0;

next(stage2) := stage1;

init(out.valid) := 0;

next(out) := stage2;

```

We'll include a refinement map for each intermediate delay stage, similar to the maps for the input and output:

```

layer spec: {

if(stage1.valid) stage1.data := bytes[stage1.idx];

if(stage2.valid) stage2.data := bytes[stage2.idx];

}

```

When verifying the output of one stage, we can drive the output of the previous stage from the abstract model, via the refinement map, thus decomposing the verification of each stage into a separate problem. Open this version in vw and select, for example, the property out.data[0]//spec. That is, we want to verify the final output against the refinement map. Select the Cone page, and notice that to define the data outputs of the stage2, SMV has chosen the layer **spec**, rather that the implementation definition. The number of state bits remaining (51) is still larger than in the previous case, however, because **spec** doesn't give any definition of the signals **valid** and **idx**, hence these are still driven by the implementation.

If you select "Prop—Verify out.data[0]//spec", you'll observe that we can still quickly verify this property, even thought the number of state variables is larger. Nonetheless, we would like to make the verification of the last stage independent of the previous stages, to be sure we can still verify it if the previous stages are made more complex. We can do this by explicitly "freeing" the signals stage2.valid and stage2.idx, that is, allowing these signals to range over any possible values of their types. This is the most abstract possible definition of a signal, and is provided by a built-in layer called free. To tell SMV explicitly to use the free layer for these signals, we add the following declaration:

```

using

stage2.valid//free, stage2.idx//free

prove

out.data//spec;

```

Open this new version, and select property out.data[0]//spec. Note the number of state bits (in the Cone page) is now 39, as in our original problem. In fact, if you select "Prop—Verify out.data[0]//spec" you will probably get a very fast answer, since SMV will notice that the verification problem you are trying to solve is isomorphic to that of the one-stage implementation we started with. This information was saved in a file for future use when that property was verified.

To verify stage2, in the same way, we need to make similar using...prove declaration, as follows:

```

using stage1.valid//free, stage1.idx//free prove stage2.data//spec;

```

Note that we don't need a corresponding declaration for stage1, since the input signals inp.valid and inp.idx have been left undefined, and are thus free in any event. With this addition, chose "Prop—Verify all", and observe that all the properties are verified very quickly, since they are all isomorphic.

#### 4.2.3 Refinement maps as types

You may have observed that it is getting a bit tedious to refinement maps for each stage of the implementation, when they are actually all the same. SMV provides a way to avoid this by specifying abstract definitions of a signal as part of its data type. We can also give a type a parameter, so that we can specify in the type declaration which abstract object an implementation object corresponds to. A parameterized type in SMV is otherwise known as a *module*. Let's declare a type with a refinement map as follows:

```

module byte_intf(bytes){

bytes : array INDEX of BYTE;

```

```

valid : boolean;

idx : INDEX;

data : BYTE;

layer spec:

if(valid) data := bytes[idx];

```

This defines an interface type that transfers an array **bytes** of bytes according to a specific protocol. This protocol is defined by layer **spec**. Now, lets rewrite our example using this type:

```

module main(){

```

}

```

/* the abstract model */

bytes : array INDEX of BYTE;

next(bytes) := bytes;

/* the input and output signals */

inp, out : byte_intf(bytes);

/* the implementation */

stage1, stage2 : byte_intf(bytes);

init(stage1.valid) := 0;

next(stage1) := inp;

init(stage2.valid) := 0;

next(stage2) := stage1;

init(out.valid) := 0;

next(out) := stage2;

/* abstraction choices */

using stage2.valid//free, stage2.idx//free prove out.data//spec;

using stage1.valid//free, stage1.idx//free prove stage2.data//spec;

}

```

Notice that there's no need to write the intermediate refinement maps. They are part of the data type.

#### 4.2.4 The effect of decomposition

To see the effect of using refinement maps let's make two versions of our simple example, one with and one without intermediate refinement maps. We can easily do this by changing the types of the intermediate stages. To make it interesting, we'll use 32 delay stages. Here is the version with intermediate refinement maps:

```

/* the implementation */

stages : array 1..31 of byte_intf(bytes);

init(stages[1].valid) := 0;

next(stages[1]) := inp;

for(i = 2; i <= 31; i = i + 1){

init(stages[i].valid) := 0;

next(stages[i]) := stages[i-1];

}

init(out.valid) := 0;

next(out) := stages[31];

/* abstraction choices */

for(i = 2; i <= 31; i = i + 1)

using stages[i-1].valid//free, stages[i-1].idx//free

prove stages[31].valid//free, stages[31].idx//free prove out.data//spec;</pre>

```

Here is the version without intermediate refinement maps:

```

/* the implementation */

stages : array 1..31 of

struct{

valid : boolean;

idx : INDEX;

data : BYTE;

}

init(stages[1].valid) := 0;

next(stages[1]) := inp;

for(i = 2; i <= 31; i = i + 1){

init(stages[i].valid) := 0;

next(stages[i]) := stages[i-1];

}</pre>

```

```

init(out.valid) := 0;

next(out) := stages[31];

```

Note, we don't want to free any of the intermediate signals in this version. Now, open the first version, and select "Props—Verify all". It should verify all 256 properties in something like 15 seconds (depending on your machine). Now, open the second version (without refinement maps). There are only 8 properties to verify in this case (one for each output bit), bit SMV cannot verify these properties, as you may observe by select "Prop—Verify all". When you get bored of watching SMV do nothing, select "Prop—Kill Verification" (note, this may not work under Windows), and click the Cone tab. Observe that the cone contains 256 state variables, which is usually to large for SMV to handle (though occasionally SMV will solve a problem of this size, if the structure of the problem is appropriate for BDD's). Note that it is possible to construct even a fairly trivial example which cannot be verified directly by model checking, but can be verified by decomposition and model checking. Generally, when a direct model checking approach fails, it's best to look for a decomposition of the problem using refinement maps, rather than to try to determine why the BDD's exploded.

# 4.3 Decomposing large data structures

In our trivial example, we are sending an array of 32 bytes. Because we only need to consider one bit out of each byte at a time, we were able to verify the implementation without explicitly decomposing this data structure. However, cases often arise when it is necessary to consider only one element at a time of a large structure. For example, we might increase the size of our array to 1 million bytes. As we will see later, sometimes even small arrays must be decomposed in this way. One one of decomposing a large array in the abstract model is to write an array of refinement maps (we'll see a more elegant way later, in section 4.6). Each element of this array defines a given low-level signal *only* when it contains the value of the corresponding element in the abstract array. For example, let's rewrite our interface data type to use a decomposed refinement map of this kind:

```

module byte_intf(bytes){

bytes : array INDEX of BYTE;

valid : boolean;

idx : INDEX;

data : BYTE;

forall(i in INDEX)

layer spec[i]:

if(valid & idx = i) data := bytes[i];

}

```

Notice that layer **spec** is now an array, with one element for each element of the array **bytes**. The layer **spec**[i] specifies the value of **data** only when **idx** is equal to **i**, and otherwise leaves data undefined. The advantage of this refinement map is that spec[i] refers to only one element of the array bytes. Thus, the other elements will not appear in the cone when verifying it, and we have reduced the number of state variables that the model checker must handle.

Let's go back to our 3-stage delay example, and use this new definition of byte\_intf. Because we have changed the layer declarations, we also have to change the corresponding using...prove declarations. Replace these with the following:

```

forall(i in INDEX){

using stage2.valid//free, stage2.idx//free prove out.data//spec[i];

using stage1.valid//free, stage1.idx//free prove stage2.data//spec[i];

}

```

Now, when you try to open this file, you'll get an error message, something like this:

```

The implementation layer inherits two definitions of inp.data[5] ...in layer spec[31], "map7.smv", line 15

...in layer spec[30], "map7.smv", line 15

Perhaps there is a missing "refines" declaration?

```

This is because we have given many abstract definitions for inp.data without providing an implementation. By default, if there is only one abstract definition, SMV takes this as the implementation. However, if there are many abstract definitions, it is possible that these definitions are contradictory, and hence there is no possible implementation. There are several possible ways to make SMV stop complaining about this. One is to provide an actual implementation. For example, we could simply implement inp.data by a nondeterministic choice among all possible data values. This would mean, of course, that we could not then prove consistency with the maps inp.data//spec[i]. On the other hand, we don't really want to prove these, since they are actually assumptions about the inputs to our design, and not properties to be proved. One way to tell SMV this is to declare inp explicitly as an input to the design. SMV does not attempt to verify refinement maps driving global inputs. It just takes them as assumptions. If our main module is later used as a submodule in a later design, we'll have to verify these maps in the context of the larger design. Meanwhile, let's change the header of our main module to look like the following:

```

module main(bytes,inp,out){

bytes : array INDEX of BYTE;

input inp : byte_intf(bytes);

output out : byte_intf(bytes);

```

Notice we've also make bytes a parameter to the module. If we later use this module in a larger design, we can then specify what abstract data array we want the module instance to transmit. Now, open this file, and select, for example, property out.data[0]//spec[0]. You'll notice that there are now only 8 state variables in the cone, since 31 of data bits have been eliminated. Also, notice that SMV chose the layer spec[0] to define stage2.data[0], out of the 32 possible abstract definitions. This is a heuristic choice, which was made on the basis of the fact that we are verifying an abstraction in layer spec[0]. If you'd like to see

the reasoning SMV went through to arrive at this choice, select the signal stage2.data[0] and pull down "Abstraction—Explain Layer".

If you now select "Prop—Verify out.data[0]//spec[0]", you can observe that the verification is in fact faster than in the previous case. However, you'll also notice that the number of properties to prove is now very large. In fact, it is 32 times greater than before, since every property has now been decomposed into 32 cases! Select "Prop—Verify All", and you will find that the total verification time for this long list of properties is about 15 seconds, actually longer than before. Surely it is unnecessary to verify all of the 32 cases for each refinement map, since each is in effect symmetric to all the others. In fact, if we simply tell SMV where the symmetry is, we can convince it to prove only one case out of 32.

# 4.4 Exploiting Symmetry

Change the type declaration for INDEX from

```

typedef INDEX 0..31;

```

$\mathrm{to}$

```

scalarset INDEX 0..31;

```

This is exactly the same as an ordinary type declaration, except it tells SMV that the given scalar type is *symmetric*, in the sense that exchanging the roles of any two values of the type has no effect on the semantics of the program. In order to ensure that this symmetry exists, there are a number of rules placed on the use of variables of a scalarset type. For example, we can't use constants of a scalarset type, and the only operation allowed on scalarset quantities is equality comparison. In addition, we can't mix scalarset values with values of any other type. We can, however, declare an array whose index type is a scalarset. This makes it legal for us to make the type INDEX into a scalarset. Now, when SMV encounters an array of properties whose index is of scalarset type, it chooses only one case to prove, since if it can prove one case, then by symmetry it can prove all of them.

Let's see the effect of this on our example. Open the new file (with INDEX changed to a scalarset), and look in the Properties page. You'll see that there are now only properties from layer spec[0]. Pull down "Prop—Verify All", and you'll find the total verification time reduced to about a half second (a savings of a factor 32!).

We can go a step further than this, and make the type BIT a scalarset as well. This is because all of the bits within a byte are symmetric to each other. So change

```

typedef BIT 0..7;

```

$\operatorname{to}$

```

scalarset BIT 0..7;

```

and open the new file. Now, in the Properties pane, there are only three properties, one for each stage! Thus, using symmetry, we have reduced the number of properties, by a factor of  $32 \times 8 = 256$ .

# 4.5 Decomposing large structures in the implementation

Thus far, we've seen how we can decompose a large structure in the abstract model (such as the byte array in our example), and verify properties relating only to one small component of the structure. Now, we'll consider the case where we have a large structure in the implementation, and wish to consider only one component at a time. Let's keep the specification from our previous example, but design an implementation that has a large buffer that can store data bytes in transit. To make the problem more interesting, we'll put flow control in the protocol, so that our implementation can stop the flow of incoming data when its buffer is full. To implement flow control, we'll use two signals, one to indicate the sender is ready (srdy) and one to indicate the receiver is ready (rrdy). A byte is transferred when both of these signals are true. Here's the definition of this protocol as an interface data type:

```

module byte_intf(bytes){

```

```

bytes : array INDEX of BYTE;

srdy,rrdy : boolean;

idx : INDEX;

data : BYTE;

valid : boolean;

valid := srdy & rrdy;

forall(i in INDEX)

layer spec[i]:

if(valid & idx = i) data := bytes[i];

}

```

Note that the refinement map only specifies the value of the data when both srdy and rrdy are true. Our system specification is exactly the same as before:

```

module main(bytes,inp,out){

bytes : array INDEX of BYTE;

input inp : byte_intf(bytes);

output out : byte_intf(bytes);

/* the abstract model */

next(bytes) := bytes;

```

For the implementation, we'll define an array of 8 cells. Since all of the cells are symmetric, we'll define a scalarset type to index the cells:

```

scalarset CELL 0..7;

```

Each cell holds an index and a data byte. Each cell also needs a bit to say when the data in the cell are valid:

```

cells : array CELL of struct{

valid : boolean;

idx : INDEX;

data : BYTE;

}

```

We also need pointers to tell us which cell is to receive the incoming byte and which cell is to send the outgoing byte:

```

recv_cell, send_cell : CELL;

```

The implementation is ready to receive a byte when the cell pointed to by **recv\_cell** is empty (*i.e.*, not **valid**). On the other hand, it is ready to send a byte when the cell pointed to by **send\_cell** is full (*i.e.*, **valid**):

```

inp.rrdy := ~cells[recv_cell].valid;

out.srdy := cells[send_cell].valid;

```

Here is the code that implements the reading and writing of cells:

```

forall(i in CELL)init(cells[i].valid) := 0;

default{

if(inp.valid){

next(cells[recv_cell].valid) := 1;

next(cells[recv_cell].idx) := inp.idx;

next(cells[recv_cell].idx) := inp.data;

}

} in {

if(out.valid){

next(cells[send_cell].valid) := 0;

}

}

out.idx := cells[send_cell].idx;

out.data := cells[send_cell].data;

```

For the moment, we will leave the pointers recv\_<cell and send\_cell undefined, and thus completely nondeterministic. This will allow us to cover all possible policies for choosing cells. Later, we can refine these signals to use a particular policy (*e.g.*, round-robin) without invalidating our previous work.

Finally, having defined our implementation, we will define a refinement map for the structure cells so that we do not have to consider the entire array at once. In fact, this refinement map almost defines itself, given the way the data structure cells is encoded. We want to say that if a cell i is valid, then its data is equal to the element of bytes pointed to by its index idx. Here is the refinement map:

```

forall(i in INDEX)

layer spec[i]:

forall(j in CELL)

if(cells[j].valid & cells[j].idx = i) cells[j].data := bytes[i];

```

Note that once again, we have decomposed the map into separate indices. If cell j's index is i, then cell j contains byte i from the abstract array.

Now that we have defined each cell's contents in terms of the abstract model, we can verify each cell separately. We can then assume that all the cells are correct when we verify the implementation output. Open this file, and notice that in the properties pane, there are just two properties: cells[0].data[0]//spec[0] and out.data[0]//spec[0]. All the other properties are equivalent to one of these by symmetry. Try "Prop—Verify All" to check that in fact our refinement is correct. Now select cells[0].data[0]//spec[0] in the Properties pane, and the click on the Cone tab. There are 15 state variables in total for this property. Notice that once again SMV has chosen layer spec[0] to drive inp.data[0], since this is the layer we are verifying. Because of the decomposition we have used, data bits from only one cell and one element of the bytes array appear in the cone. In fact, most of the state bits come from the valid bits of the cells. These are included in the correctness of cell 0 does not actually depend on the valid bits of the other cells. We should be able to free them and still verify the property. To do this, add the following declaration to the program:

```

forall(i in INDEX) forall(j in CELL) forall(k in BIT)

using cells//free, cells[j]

prove cells[j].data[k]//spec[i];

```

This declaration probably requires some explanation. First, even though we are only interested in proving one property, cells[0].data[0]//spec[0], we give a prove declaration for cells[j].data[k]//spec[i], for all i,j,k. This is because we are not allowed to use constants of a scalarset type in the program. Second, in order to free the signals in all the cells *except* cell j, we specify cells//free, indicating that all components of cells should use the free layer, and then specify cells[j] to override this choice for the specific case of cell j. In a using declaration, a signal name without a layer indicates the implementation definition of that signal.

Open this version and select the property cells[0].data[0]//spec[0]. The number of state variables should now be 8 rather than 15, since the valid bits for the other cells are now free variables. Select "Prop—Verify cells[0].data[0]//spec[0]" and observe that our hypothesis is confirmed – the correctness of cell 0 is preserved, even when we free the state of the other cells. Also note that verification time is reduced.

Note, that by freeing some signals, we have decreased the number of state variables in the cone, we have also increased the number of "combinational" variables. These are variables that act as free or constrained inputs to the model. We can go a step further and substitute the "undefined" value for these bits. This is very much like an "X" value in a logic simulator. For example:

```

0 & undefined = 0

1 & undefined = undefined

0 | undefined = undefined

1 | undefined = 1

```

Using the undefined value has the advantage that no combinational variables will introduced, since these signals are given the constant value "undefined". The difficulty is that, as in a logic simulator, these undefined values can propagate widely, giving a pessimistic result – we may find that a counterexample is produced to the property using undefined values, even though the property is actually true. However, we can never "prove" a false property by introducing undefined values.

We can set signals to the undefined value using a predefined layer called undefined. For example, replace cells//free in the using ... prove declaration above with

#### cells//undefined

This will cause the signals that were previously freed to be given the undefined value instead. Open the new file and select the property cells[0].data[0]//spec[0]. Notice in the Cone pane that the other valid bits are no longer combinational variables. Thus we have eliminated 7 combinational variables from the cone. On the other hand, you can observe by selecting "Prop—Verify cells[0].data[0]//spec[0]" that the property is still provable under this weaker assumption about the environment.

Finally, let's go back to the other property we need to prove in this example, which is that the outputs are correct with respect to the specification (out.data[0]//spec[0]). Select this property in the Properties pane, and observe that there are still 49 state variables in the cone. This is because, although our refinement map drives the data value for each cell from the abstract model, the control bits idx and valid for each cell are still driven from the implementation. This is not a problem for us, since BDD's come to our rescue in this case. You can confirm this by selecting "Prop—Verify out.data[0]//spec[0]". This verification should take less than 2 seconds. Nonetheless, if this were not the case, we could reduce the number of state bits by freeing the cells' control bits. That is, our refinement map provides that the data in a cell are correct, for any values of the control bits valid and idx. So let's add the following declaration to the program:

```

forall(i in INDEX) forall(j in CELL) forall(k in BIT)

using cells[j].idx//free, cells[j].valid//free

prove out.data[k]//spec[i];

```

Open the new version and select the property out.data[0]//spec[0]. Notice that the number of state bits is now reduced to 1, a single bit of the abstract array. The verification time is also reduced, as you can observe by selecting "Prop—Verify out.data[0]//spec[0]".

### 4.6 Case analysis

Suppose that we have a condition p, and we would like to show that p holds true at all times. For any particular variable x, we could break the problem into cases. For each possible value of  $\mathbf{x}$  of  $\mathbf{x}$ , we could show that condition  $\mathbf{p}$  is true at those times when  $\mathbf{x} = \mathbf{v}$ . Since at all times  $\mathbf{x}$  must have one of these values, we can infer that  $\mathbf{p}$  must be true at all times.

SMV has a special construct to support this kind of case analysis. It is especially useful for compositional verification, since for each case we can use a different abstraction of the system, including different components in the verification. This allows us to break large verification problems into smaller ones.

The above described case analysis is expressed in SMV in the following way:

forall (v in TYPE)

subcase q[v] of p for x = v;

Now suppose that p is some temporal assertion G cond, where cond is any boolean condition. The above declaration effectively defines a collection of properties q[v], as if we had written

```

forall (x in TYPE)

q[v] assert G (x=v -> cond);

```

That is, each q[v] asserts that p holds at those times when x = v. Clearly, if q[v] holds for all values of v, then p holds. Thus, SMV is relieved of the obligation of proving p, and instead separately proves all the cases of q[v]. Note that if TYPE is a scalarset type, we may in fact have to prove only one case, since all the other cases are symmetric.

#### 4.6.1 A very simple example

Now, let's look at a trivial example of this. Let's return to our very simple example of transmitting a sequence of bytes. Here is the specification again:

```

scalarset BIT 0..7;

scalarset INDEX 0..31;

typedef BYTE array BIT of boolean;

module main(){

/* the abstract model */

bytes : array INDEX of BYTE;

next(bytes) := bytes;

/* the input and output signals */

inp, out : struct{

valid : boolean;

idx : INDEX;

data : BYTE;

}

```

```

/* the refinement maps */

layer spec: {

if(inp.valid) inp.data := bytes[inp.idx];

if(out.valid) out.data := bytes[out.idx];

}

```

And let's use our original very trivial implementation:

```

init(out.valid) := 0;

next(out) := inp;

}

```

That is, the output is just the input delayed by one time unit.

Note that our specification (layer **spec**) says that at all times the output value must be equal to the element of array **bytes** indicated by the index value **out.idx**. We would like to break this specification into cases and consider only one index value at a time. To do this, we add the following declaration:

```

forall (i in INDEX)

subcase spec_case[i] of out.data//spec for out.idx = i;

```

In this case, the property we are splitting into cases is out.data//spec, the assignment to out.data in layer spec. The resulting cases are out.data//spec\_case[i]. Note, however, that in the subcase declaration, we only give a layer name for the new cases, since the signal name is redundant. This declaration is exactly as if we had written

```

forall (i in INDEX)

layer spec_case[i]:

if (out.idx = i)

out.data := bytes[out.idx];

```

except that SMV recognizes that if we prove out.data//spec\_case[i] for all i, we don't have to prove out.data//spec. Run this example, and look in the properties pane. You'll see that out.data//spec\_does not appear, but instead we have out.data//spec\_case[0]. Note that only the case i = 0 appears, since INDEX is a scalarset type, and SMV knows that all the other cases are symmetric to this one. Now look in the cone pane. You'll notice that all of the elements of the array bytes are in the cone. This is because the definition of inp.data in layer spec references all of them. However, all of them except element 0 are in the undefined layer. This is a heuristic used by SMV: if a property references some specific value or values of a given scalarset type, then only the corresponding elements of arrays over that type are used. The rest are given the undefined value. You might try clicking on element bytes[1] and choosing Abstraction|Explain Layer to get an explanation of why this signal was left undefined. You can, of course, override this heuristic by explicitly specifying a layer for the other elements. In this case, however, the heuristic works, since property out.data//spec\_case[0] verifies correctly.

#### 4.6.2 Using case analysis over data paths

Now we'll look at a slightly more complex example, to show how case analysis can be used to reduce a verification problem to a smaller one, by considering only one path that a given data item might take from input to output. This technique is quite useful in reasoning about data path circuitry.

We'll use essentially the same specification as before, but in this case our implementation will be the array of cells that we used previously when discussing refinement maps (section 4.5). We have an array of cells, and each incoming byte is stored in an arbitrarily chosen cell. Recall that the specification in this case has to take into account the handshake signals. That is, the data are only valid when both sdry and rrdy are true:

```

/* the abstract model */

bytes : array INDEX of BYTE;

next(bytes) := bytes;

/* the input and output signals */

inp, out : struct{

srdy,rrdy : boolean;

idx : INDEX;

data : BYTE;

}

/* the refinement maps */

layer spec: {

if(inp.srdy & inp.rrdy) inp.data := bytes[inp.idx];

if(out.srdy & out.rrdy) out.data := bytes[out.idx];

}

```

For reference, here is the implementation again:

```

/* the implementation */

cells : array CELL of struct{

valid : boolean;

idx : INDEX;

data : BYTE;

}

recv_cell, send_cell : CELL;

inp.rrdy := ~cells[recv_cell].valid;

out.srdy := cells[send_cell].valid;

```

```

forall(i in CELL)init(cells[i].valid) := 0;

default{

if(inp.srdy & inp.rrdy){

next(cells[recv_cell].valid) := 1;

next(cells[recv_cell].idx) := inp.idx;

next(cells[recv_cell].idx) := inp.data;

}

} in {

if(out.srdy & out.rrdy){

next(cells[send_cell].valid) := 0;

}

}

out.idx := cells[send_cell].idx;

out.data := cells[send_cell].data;

```

0

Recall that in the previous example, we wrote refinement maps for the data in the individual cells, in order to break the verification problem into two pieces: one to show that cells get correct data, and the other to show that data in cells are correctly transferred to the output. Now, we will use case analysis to get a simpler decomposition, with only one property to prove.

Our case analysis in this example will be a little finer. That is because we have two arrays we would like to decompose. One is the array of bytes to transfer, and the other is the array of cells. We would like to consider separately each case where byte[i] gets transfered through cell[j]. In this way, we can consider only one byte and one cell at a time. This is done with the following declaration:

```

forall (i in INDEX) forall (j in CELL)

subcase spec_case[i][j] of out.data//spec

for out.idx = i & send_cell = j;

```

Notice that our case analysis now has two parameters. Each case is of the form out.idx = i & send\_cell = j where i is an INDEX and k is a CELL. We can, in fact, have as many parameters in the case analysis as we like, provided we write the condition in the above form. SMV recognizes by the form of the expression that the cases are exhaustive.